Other Parts Discussed in Thread: TPS3808-Q1, TPS3808, AMC1311

Hi,

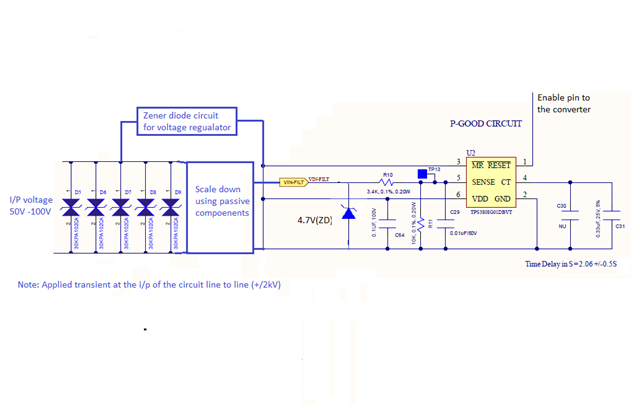

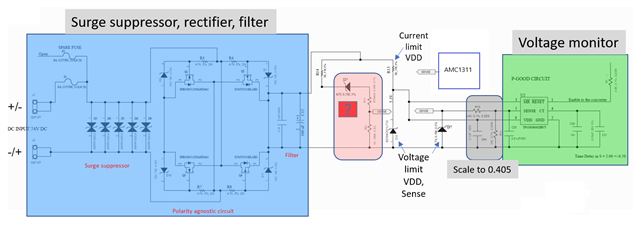

In my circuit i have connected the reset output to the enable pin converter.

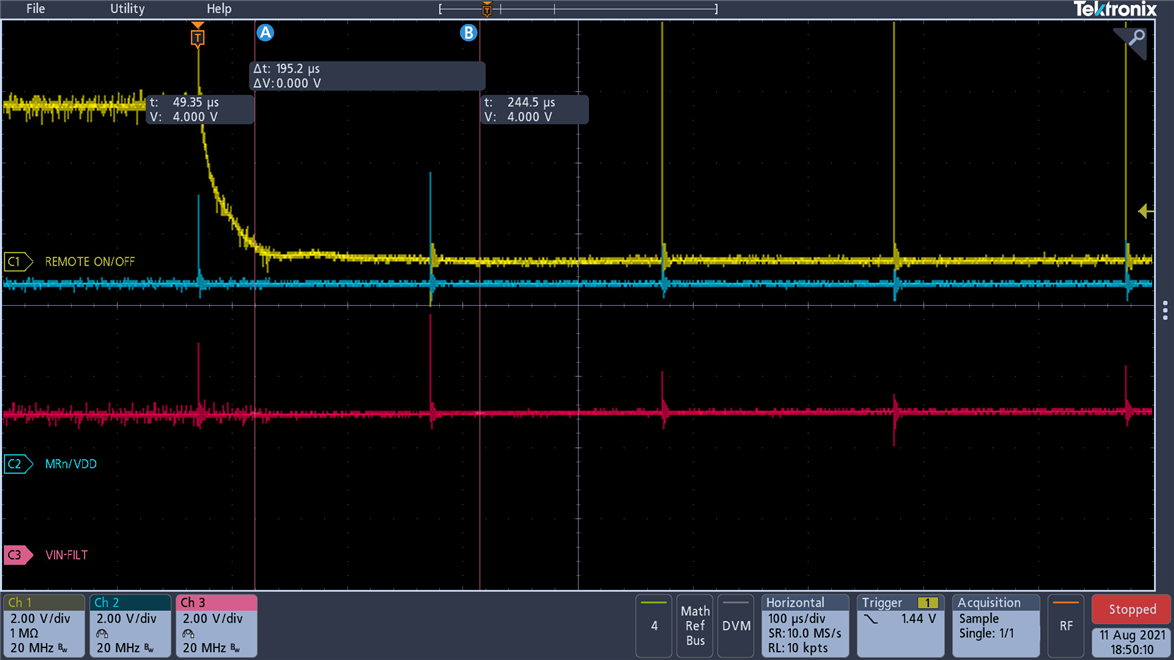

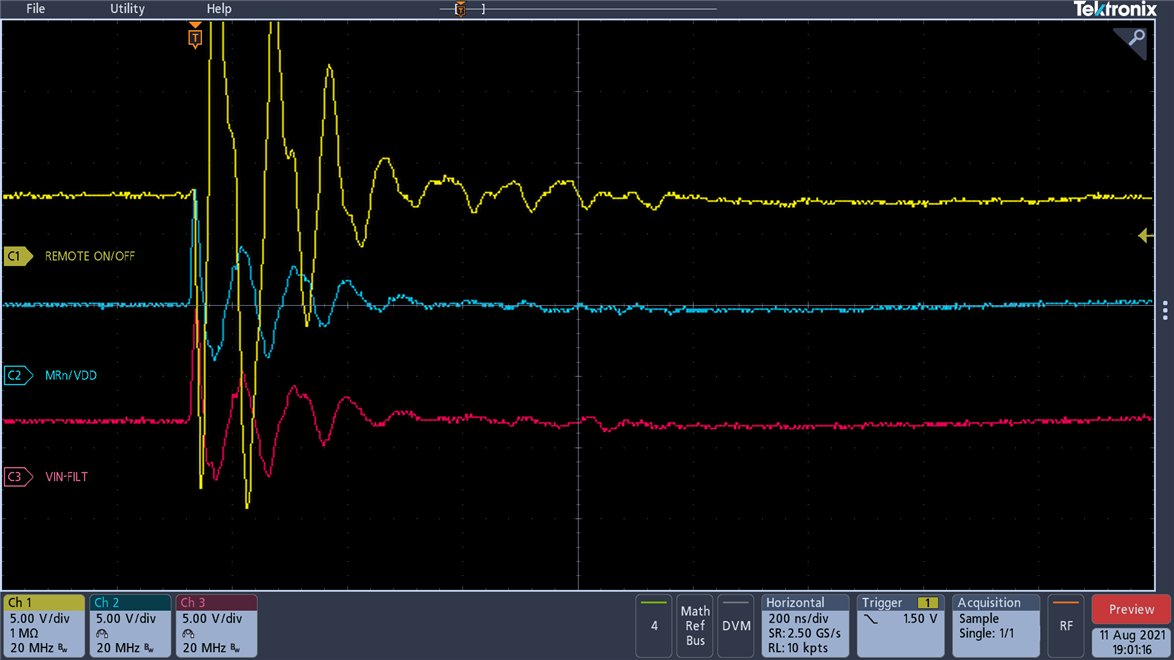

Condition is shown below,

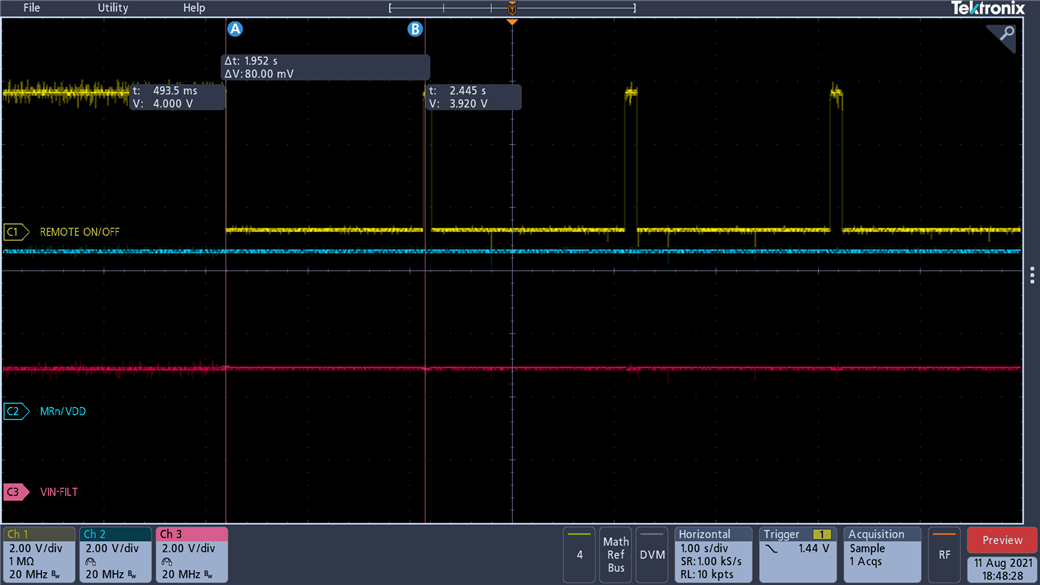

VDD = 5.1V, MRn = VDD, Gnd = 0V.

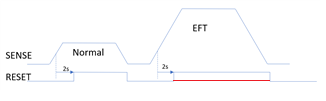

SENSE voltage < Vit reset get asserted = Disable

SENSE voltage > Vit after time delay of 2s reset get deasserted = Enable.

In normal operation works good as per the above condition.

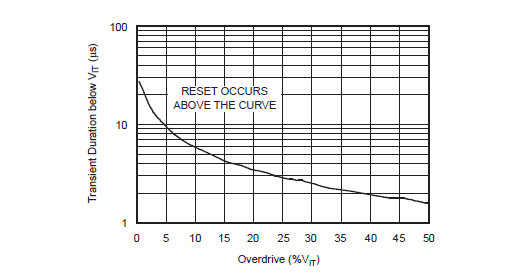

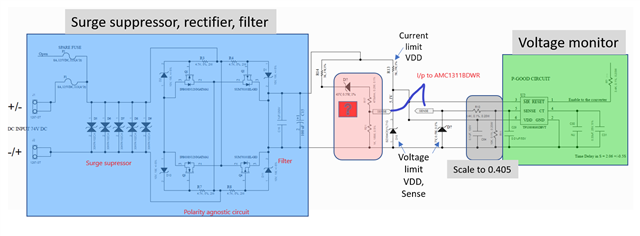

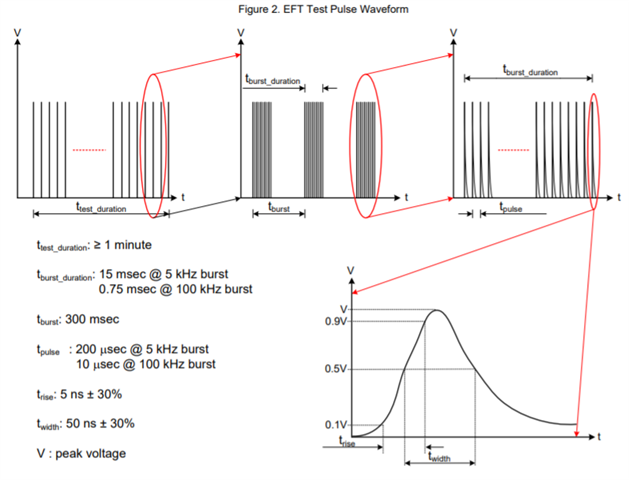

Problem: When EFT transient is applied across line to line, The converter is disable & resume to work after EFT duration of 60s. Circuit is posted in the image below,

There is set of transorbs right at the input of circuit (30KPA102CA) & 4.7V zener diode at the input of SENSE voltage Pin with 10nf bypass capacitor.

Possible solution to pass the EFT transient test suggestions.

Possible