Hi,

We'd like to better understand the AOLD protections setting if you're able to assist.

We find that on brief (<500ms) load current transients, out pack shuts down (DSG/CHG FET turns off), setting the AOLD and AOLDL flags.

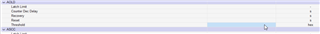

Changing the Counter Dec Delay time appears to make no difference - it is currently set to 10s.

Is there a way to set a delay on this feature, so it isn't activated unintentionally by brief transients?

I was able to adjust the Current threshold, and did see a corresponding increase in the transient the pack could withstand, as expected. However it'd be good to also employ a time delay as our load is quite dynamic during operation.

Second question: Are you able to suggest a source of supply for the BQ40Z80? We're looking to buy 100-250 to support our next build (though ANY quantity would help!), and stock levels on your site and digikey are zero. I'd prefer not to have to redesign our battery pack to use a different device at this stage of development, as you could well understand.

thank you,

regards,

Daniel