Hi,

I'm looking at using the TPS62913 to provide a 3A 1.35V rail.

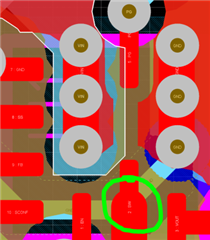

Looking at the land pattern recommendation, the SW node is 0.2mm x 1.0mm. Using online PCB trace calculator tools, it looks like a trace that's only 0.2mm will struggle maintain 3A of current - even with very high plating options.

Am I right in thinking this land pattern is OK because the pins quickly fan out into large inductor pads? Is there any way to verify this is OK in Webench - I recall there used to be thermal simulation option but this doesn't appear available for this device.

Any advice would be greatly appreciated.

Many thanks