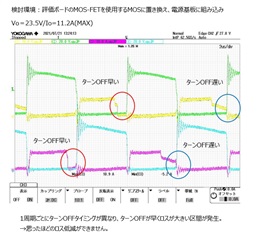

Condition : TI UCC24624 EVM

Modified point: updated MOSFET

Power supply condition: Vo(MAX) 23.5V/ IO(Max) 11.2A

Original waveform was shown below and I could see turn off timing made more bigger loss thru body diode.

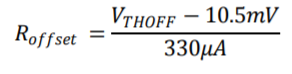

Then my customer adjusted Roffset value(VSS terminal). It has been improved efficiency by Roffset value change.

I could understand turn off as early timing but please let me know reason why 1 of 2 turnoff time became earlier?

Another question is What are the side effects of increasing the VSS terminal resistance too high?