Hi team,

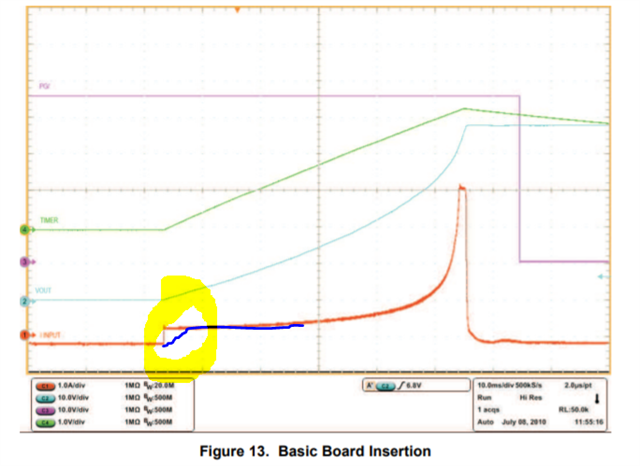

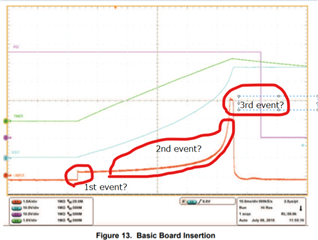

I'd like to know fig 13 in p.14.

Could you tell me the details of this operation?

I think it has three events.

I'd like to hear about each event.

Sincerely.

Kengo.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.