Device and condition:

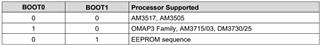

a) TPS65910A3A1

b) Boot1=H and Boot2=L

c) VRTC is OK (1.8V)

d) PMIC_HOLD = H

But, VDAC and subsequent other outputs are not ON.

I have some doubts to clarify

a) High Level is OK for PMIC_HOLD or Rising Edge is needed

b) VREF value is little bit higher, ie, 0.880V, instead of (0.850V+/-1%). Is there any way to bring down by 30mV. Does it affect VBAT 3V threshold for ON.

c) On AM335x, PMIC_EN is bit early, is there any way to delay by 2 to 3ms. Exact which input has control over PMIC_EN generation on AM335x, RTC_PORZ or EXT_WAK or VRTC etc..