Other Parts Discussed in Thread: LM5143

Hi,

In one of our recent design we are using PMIC TPS65086401RSKT to power up the Xilinx FPGA ZU3. The Power architecture is we have a 24Vdc power as input to this board which is first fed to a buck (LM5143) to generate 12Vdc. This 12Vdc is the input to PMIC to generate different power rails required by ZU3.

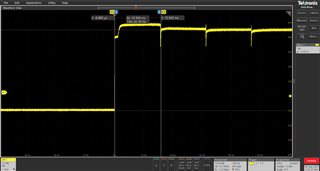

The power-up sequence is as in below snap shot. (The load switch used is TPS22959DNYR). attached is the draft schematics for this block alone. The voltage rails (VCC_5V_PMIC, VCC_12V are generated using LM5143)

The issues that i am facing are,

1) During the board bring up , since all the power rails of the FPGA are not up yet, because some of the rails are sequenced using GPOx's and which are not configured. Is there a way to configure this PMIC (GPOx's) without using I2C programming? Manual method. (As of now none of GPOx's are giving any output, so my sequence is not getting completed).

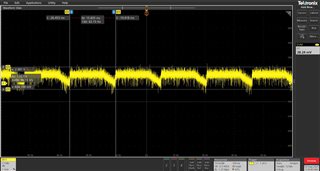

2) Since CTL1 is at 3V3 (with input VSYS=12V, LDO3V3 available), The Buck1 out is available, but the waveform looks something like this, and from one of the post in this forum I came to know that this pattern is due to Power Fault. So how can this power fault occur? ( I mean i checked for any shorts with GND but none) . The voltage reading from the scope was around 1V75 (ignore DVM readings from the snap).

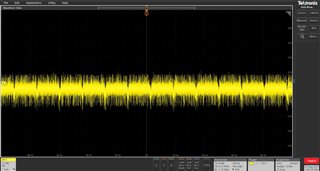

3) I am also able to see Buck2 op. The voltage reading is around 0V865 from the scope.

4) as per our sequence the Buck 6 should have been up (with CTL3 = LDO_3P3, CTL2 = GND). But its not showing any voltage.

Can you support me in debugging these issues ? Let me know if you need any other details.

With regards,

Sandeep P