Other Parts Discussed in Thread: TPS568230, TPS54519

Hello,

I have a question on TPS568230EVM layout.

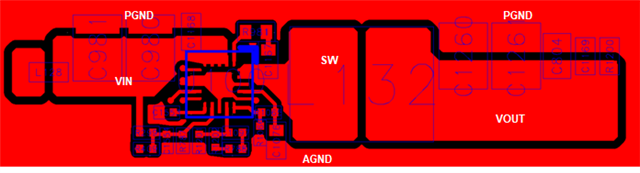

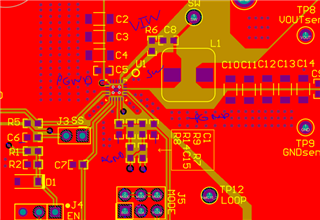

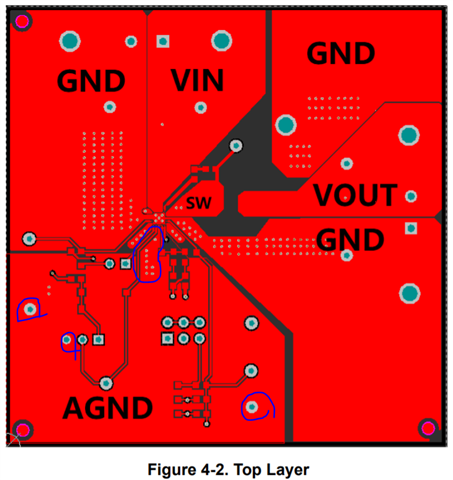

When I look at the top layer :

- GND plane (pin 7, 8, 18) and AGND plane (pin 13) are separated, and should be connected in a single point

- AGND pin should not connect to thermal pad

- Those layout practice is for preventing switching noise conducting from GND to AGND

But here comes my questions :

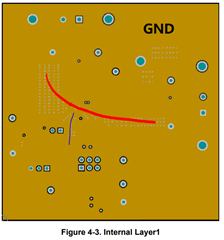

AGND and GND look completely separated in the top layer and connected in the layer 2 (GND plane) thru many vias. (I mark with blue color on the image above) I wonder how this helps to decouple the noise from GND to AGND.

To my knowledge, AGND and GND are separated at the top layer just like the EVM, and connected thru a short trace of thru a 0ohm resistor, so that the noise is hard to be injected to AGND plane. But it looks the connection to GND plane thru many vias cannot effectively isolate AGND from GND switching noise. Could you help me to understand the recommendation layout here?