Hi

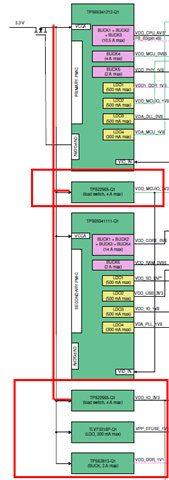

The customer does not operate PMIC during the board test with PDN-0BX.

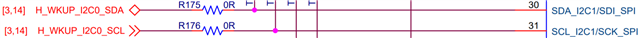

Please review if there is a problem with the schematic.

Delete Schematic.

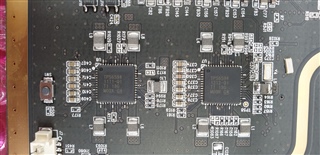

1. TPS65941212RWERQ1

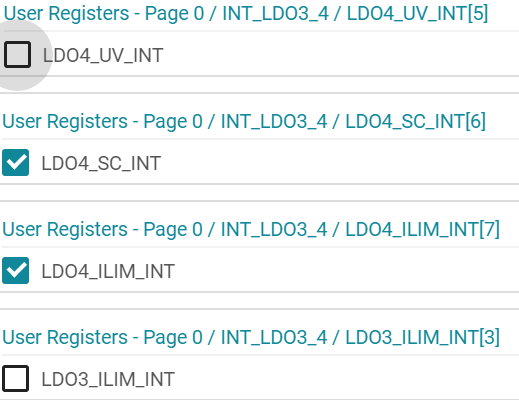

VOUT_LDOVINT : 1.8V output.

VOUT_LDORTC: 1.8 V output.

Other BUCK and LDO: Not output.

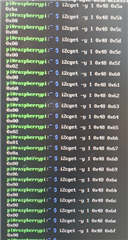

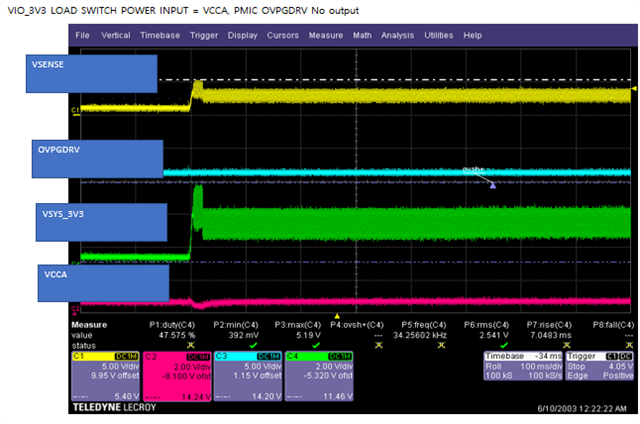

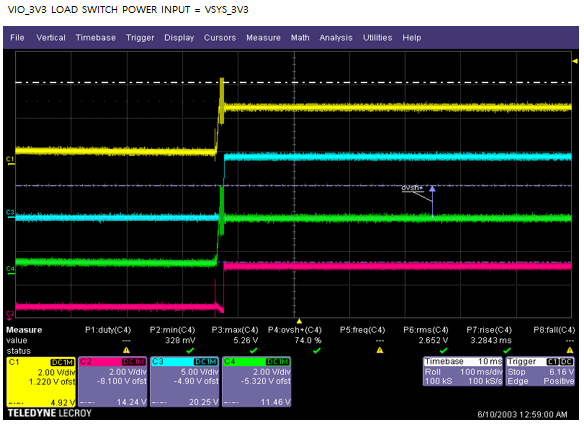

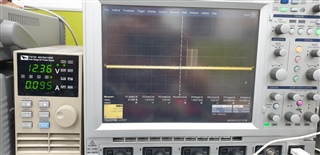

Note: As shown in the attached screenshot, GPIO3 (EN_MCU3V3_LDSW) moves for about 1 second and then falls to LOW.

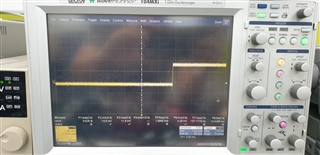

TPS65941212RWERQ1 RSTOUT Pin (GPIO11) waveform.

2. TPS65941111RWERQ1

VOUT_LDOVINT : 1.8V output.

VOUT_LDORTC: 1.8 V output.

Other BUCK and LDO: Not output.