Other Parts Discussed in Thread: UCC28951, UCC28950, UCC2895

Hello TI.

I am stuck with my DC-DC converter based on UCC3895. Basically, my circuit is almost the same as in the datasheet. The problem is that under light load (~2W) converter is unstable (crackle noise, rapid duty cycle changes). @50W load everything fine.

I have been told that such a problem can occur due to the poor slope compensation circuit. Here as I understand this phenomenon: As under light load there is almost no CS signal converter works only using ramp, generated by the slope compensation circuitry. This ramp looks quite poor because it doesn't rump up from zero and has DC bias which may cause unstable operation when EAOUT voltage is near this DC bias of the rump. Also, no-load comp kicks in.

Can you confirm that it makes sense or am I wrong with this explanation?

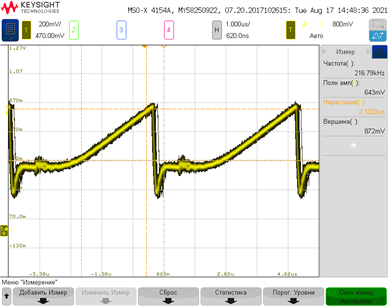

Modeled slope comp:

This is measured voltage on ramp pin when only PWM controller enabled. No HV at the input.

Also, I have some questions about slope compensation circuitry in datasheet.

1) P.39 of the DS «The 10-kΩ resistor RRB provides approximately 250-mV offset bias. The value of this resistor may be adjusted up or down to alter the point at which the internal no load comparator trips»

So how exactly can it alter the point at which the no-load comparator trips if the no-load comparator is directly connected to the EAOUT pin and 0.5/0.6 reference?

2) Formula #118 at p.38 it probably should have Msum instead of Mmag at the denominator?

3) What amplitude value and shape should have proper slope compensation to ensure robust operation within full load range 0A up to Imax? How can I estimate Rsum value?

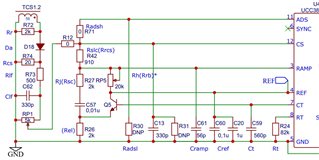

Schematic included.