Hi expert,

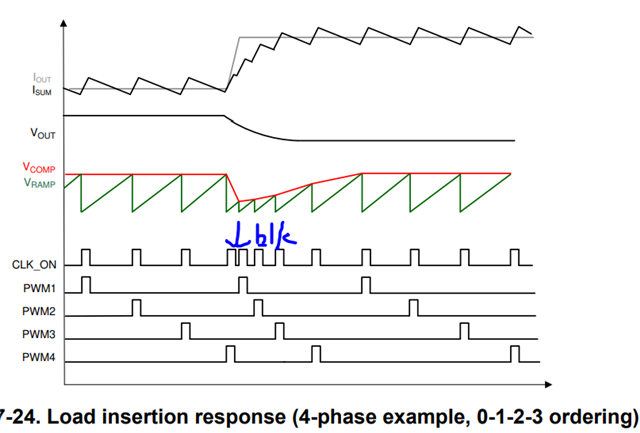

when operating in 2-phase interleaving mode, I'm interested in what would happen during load transient.

For example, when very large and high slew-rate load step-up comes, the control loop easily goes into saturation, what is the behavior of 2 phase switching? Non-linear like phase overlap, or with a blanking time between two phases?

As you know, in ACOT control, switching frequency would go up to very high when load inserts, any limitations of highest switching frequency?