Hi Team,

Here are two questions about the unused BUCK FB pin.

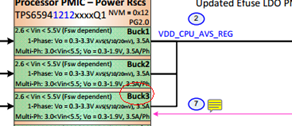

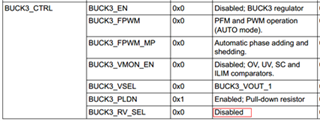

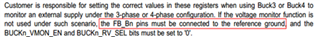

1. in PDN-0B, FB3 is used to monitor the VDDS_DDR. However, in SLVC32, the default NVM setting is to disable this feature(BUCK3_RV_SEL and BUCK3_VMON_EN). Which one is correct?

2. In the Checklist file, it is mentioned that unused FB pins can be connected to VCC or GND. however, according to TPS6594 datasheet, it must be tied to GND. Which one is correct?.

B&R

Lijia