Other Parts Discussed in Thread: TPS54020

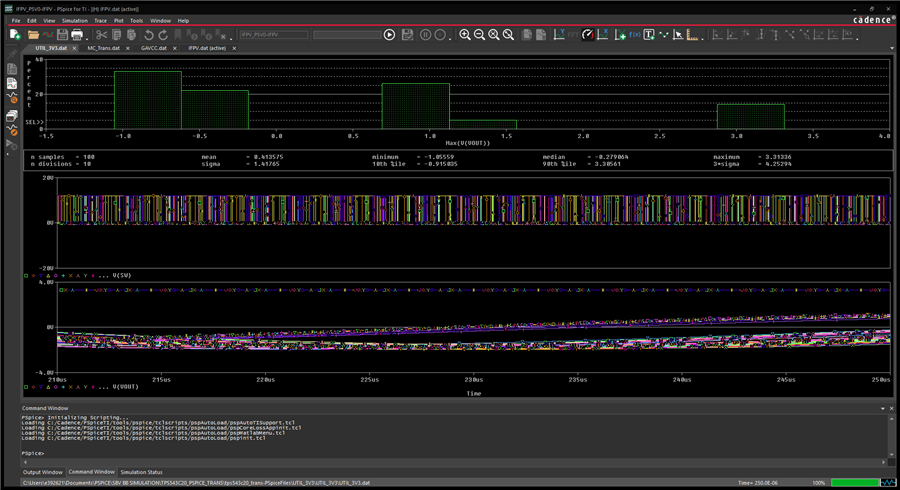

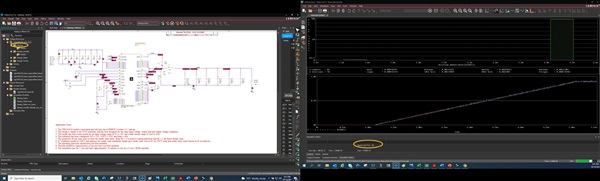

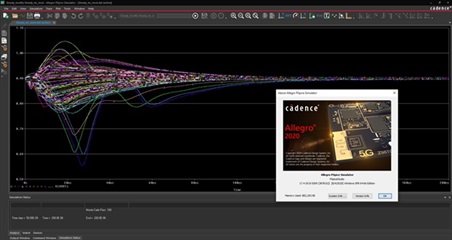

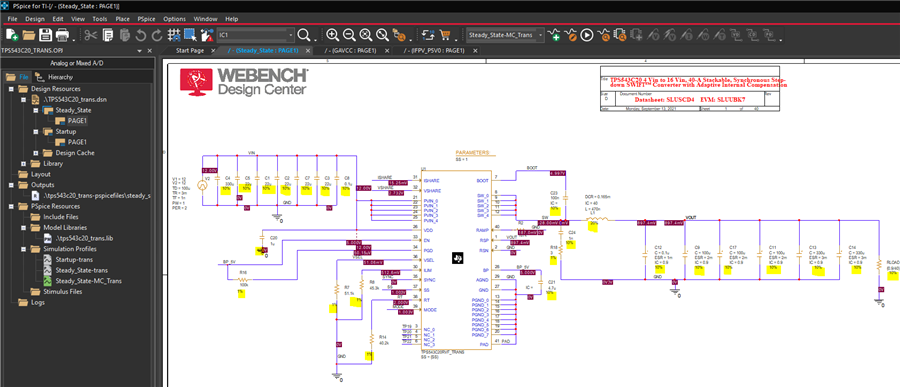

When I ran the TPS543C20 "steady_state" example model that downloaded from the TI site, PSPICE results ran OK by itself. However, if I added the tolerance at each component and ran the MC analysis, the outputs V(VOUT) varied all over the place. I ran this example because it is supposed to be the "golden circuit" and I tried to compare this to my other circuits which have the same issues. The circuit is so sensitive that if any component values change slightly, the circuit will fail. Please advise. The following is the detailed problem explanation.

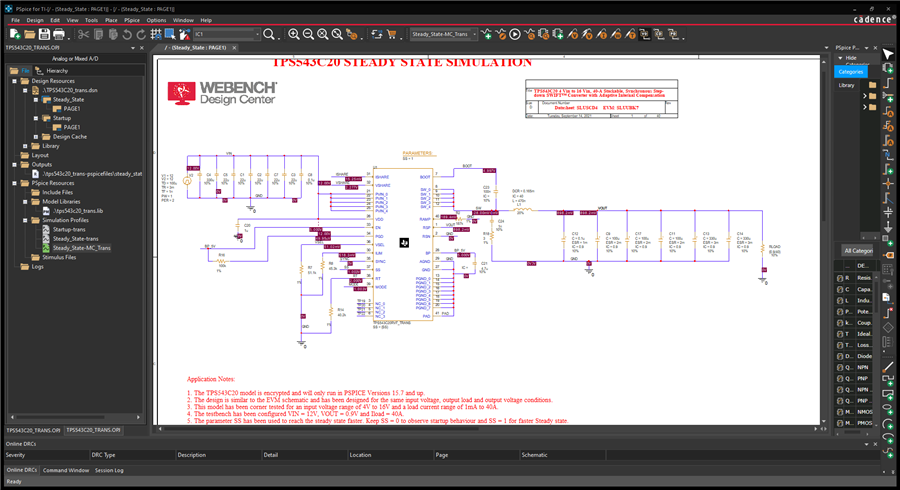

Monte Carlo Analysis with TPS543C20 Steady_State Example Model Issue

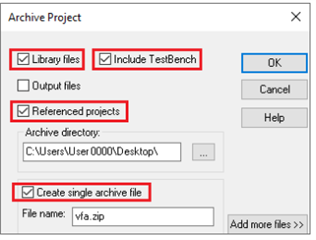

- I downloaded the PSPICE model from TI site.

- Open the PSPICE project and run the project file.

- The “included” example Steady_State model runs OK by itself. I then added the tolerance at each component and start the Monte Carlo with 100 runs.

Problems:

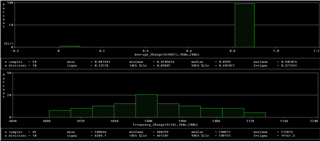

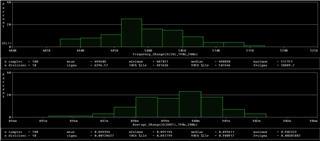

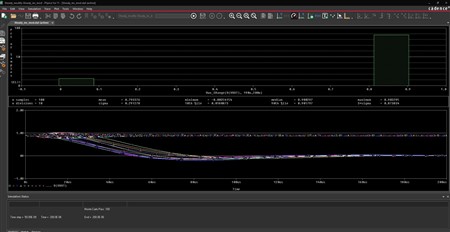

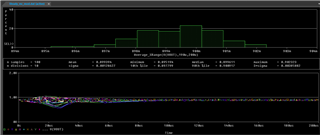

The V(VOUT) output value varies from 0 to 0.9V. The normal distribution of 0.9V is supposed to be the expected values.

The I(RLOAD) varies from 0A to 40A.

The V(SW) stops (0V) in most of the runs.

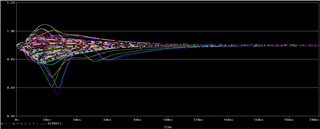

- The reason I found this problem is because I ran a lot of my circuits and they have the same issues. If I vary any component values slightly, the output voltage will failed by going to zero and the switching pulses will stop.

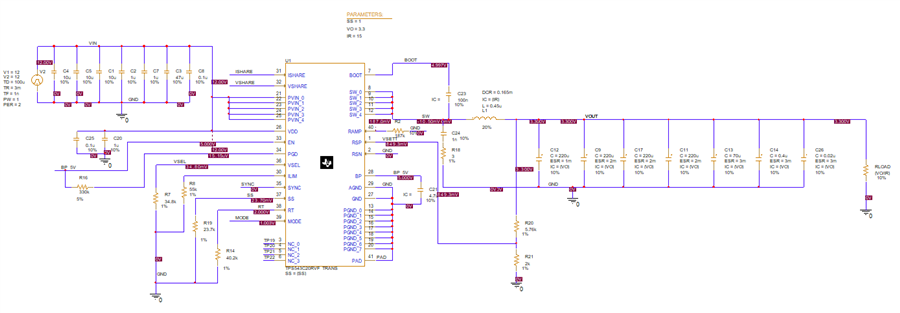

My other 12V to 3.3V 15A Circuit