customer having issue with TPS7A26 power/reset circuit performance.

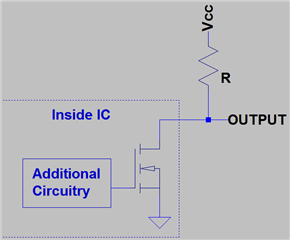

datasheet indicates PG floats to the pull up voltage when Vout exceeds 93% of the targeted Vout voltage, and PG uses open drain to pull low when Vout drops below 90% of the targeted Vout voltage. Is this correct?