Dear Expert ,

Good day!

Our customer using a LM5046 PSFB with these conditions :

- Current mode control

- External SYNC

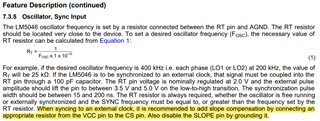

In this case, TI recommends to ground the SLOPE pin and to put a resistor for slope compensation between VCC pin and CS pin in the datasheet 7.3.5. But it seems like the CS pin is not supposed to bother about slope compensation whereas the RAMP pin should but nothing is said about RAMP pin.

On all application designs, the RAMP pin is linked to the CS pin with a resistor but never have I seen a resistor between VCC and CS !

My question is : in case of external sync in current mode control, if we ground SLOPE pin, how should I manage the RAMP pin and the CS pin ?

BR,

Leon.liu