Dear team:

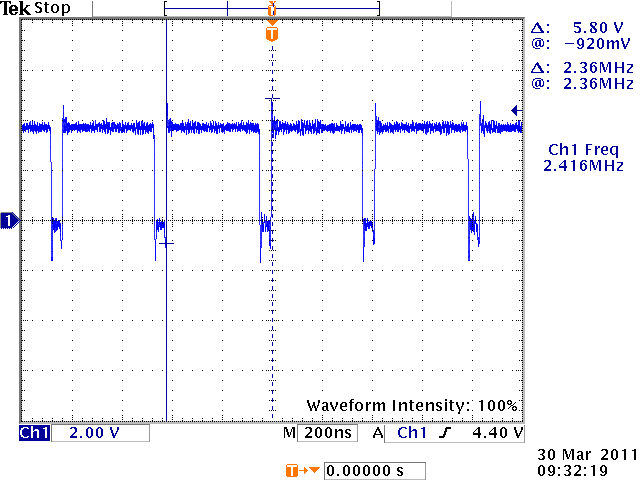

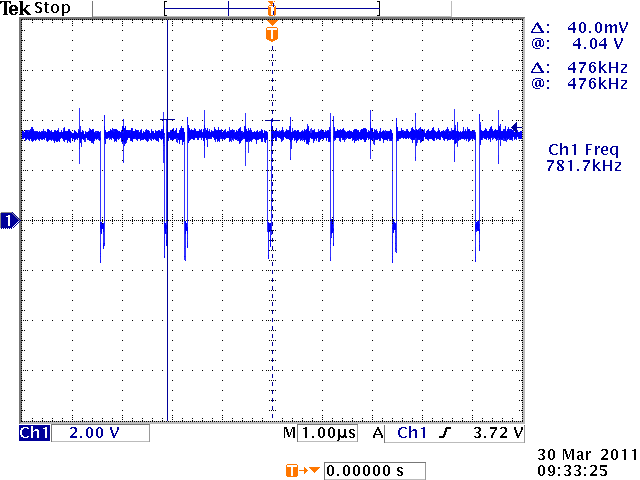

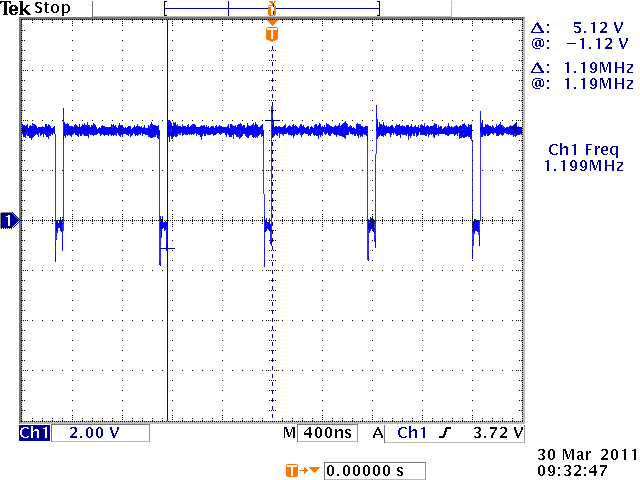

As you can see form below waveform, it is the switching waveform on our EVM board.

The test condition is VIN=4.1V and VOUT=3.3V.

The switching waveform seems like unstable when load condition over 1.5A, is it correct?

If the maximum load condition of my customer is 2A, any risk for this unstable switching waveform?

VIN=4.1V VOUT=3.3V IOUT=2A on EVM board

VIN=4.1V VOUT=3.3V IOUT=1.5A on EVM board

VIN=4.1V VOUT=3.3V IOUT=1A on EVM board