Hi,

This is a follow on from my last two posts.

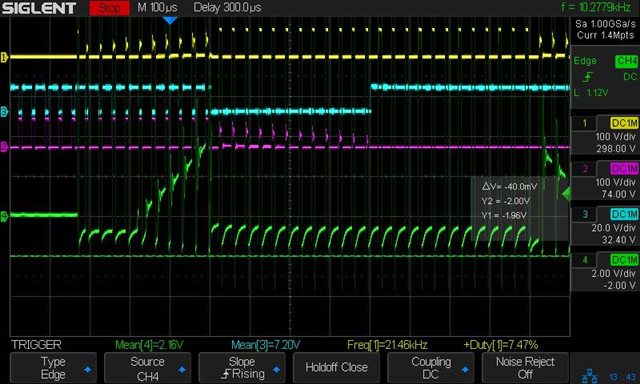

We have been testing our inverters various power levels and achieved another failure, even with, what we consider a reasonable layout, and including protections such as the additional Schottky diodes.

In our weeks worth of testing, we have had many high power runs with the inverters powered from 60 VDC, there have been no issues.

Today we increased the voltage to 72 VDC, and before our motor had even completed a single revolution, we had a damaged UCC27282 device.

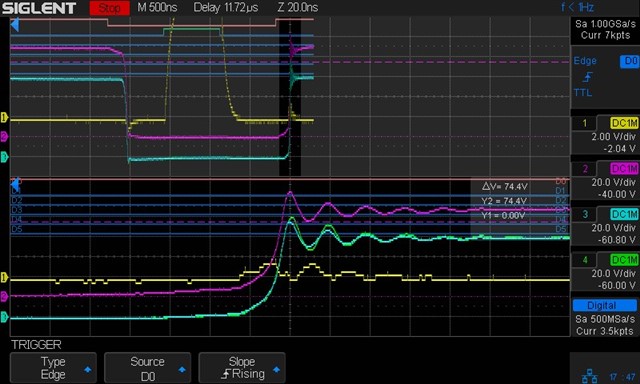

The device exhibits the following:

1. High Current Draw

2. LO output stuck high (at VCC)

3. HI output inop.

4. No charge pump capacitor voltage.

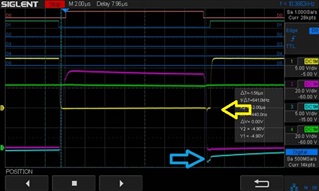

Is there anything additional TI can add as to why these drivers are so sensitive to failures when used in a motor drive application?

We will try next to remove the current sense resistor system, as this could be causing issues.

Thanks.