Hello,

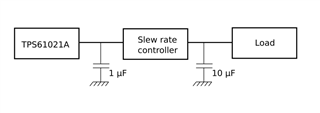

This question is related to : https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/1024194/tps61021a-slew-rate-limiter/3806487#3806487

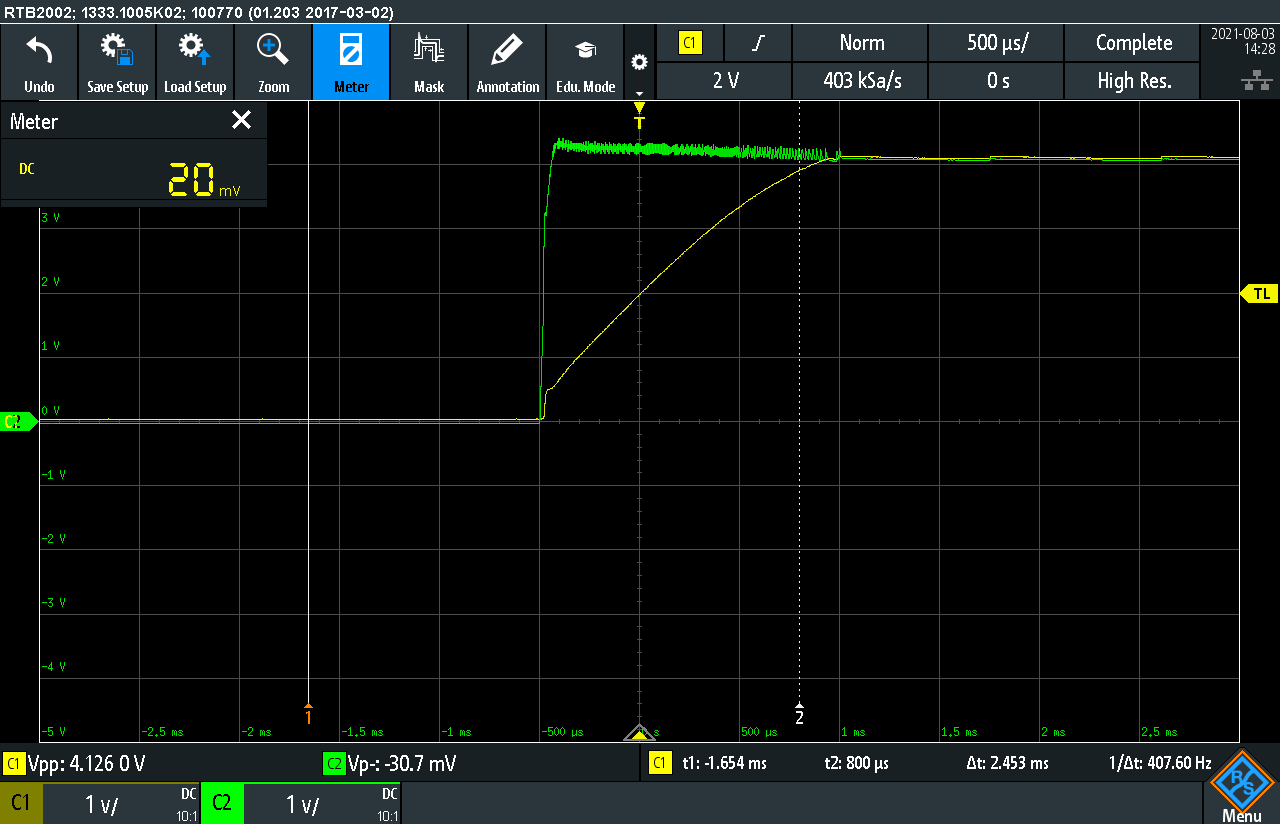

To make sure our design is stable, you proposed to test loop stability in these conditions:

- with 1uF capa, slew rate limiter and 10uF capa on output

- only 1uF capa on output

So we made some measurements for both situations with multiple input voltages (2V, 2.5V and 3V).

I would like to have your advice on the bode plots.

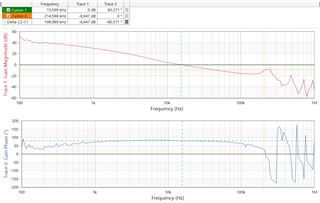

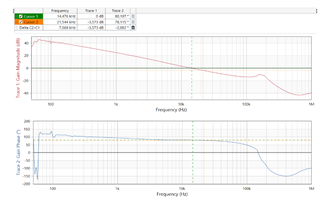

1. 1uF capa, slew rate limiter and 10uF on output

We used a 4Ohms load.

Here is the worst case with 2V input voltage :

Phase margin is 80° and gain margin 11dB.

The system is stable.

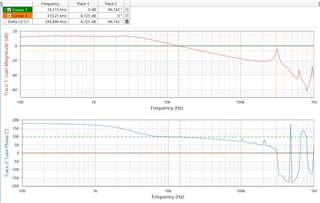

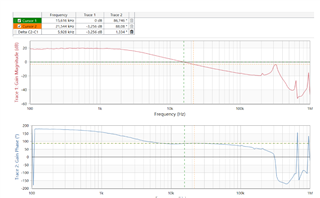

2. only 1uF capa on output

We used a lighter load of 20 Ohms.

Here is the worst case with 2V input voltage :

Phase margin is ok : 85° but gain margin is a bit low : around 5dB.

The low gain margin is due to the pic around 300kHz.

Is it something we should worry about or can we safely keep the 1uF capacitor at startup ?

Note : the method used for the measurements is described here : www.omicron-lab.com/.../App_Note_DC_DC_Stability_V3_3.pdf

Thanks for your help

Guillaume