Hi,

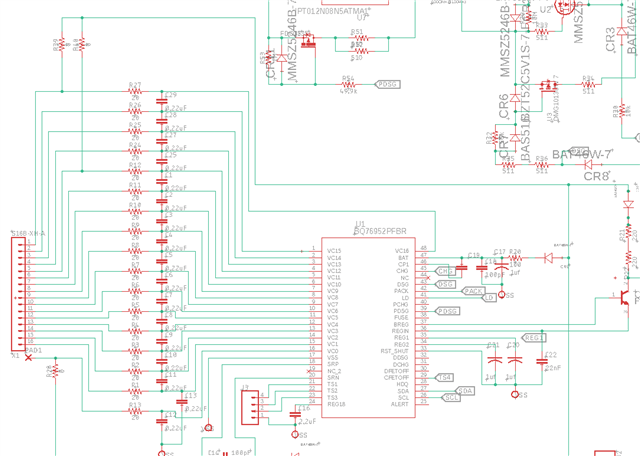

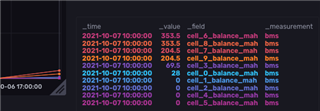

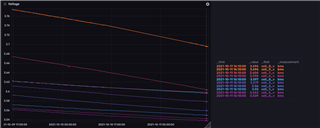

i have a 10s design with cell 1 on 0-1 and cell 10 on 15-16 with 10,11,12,13,14,15 bridged.

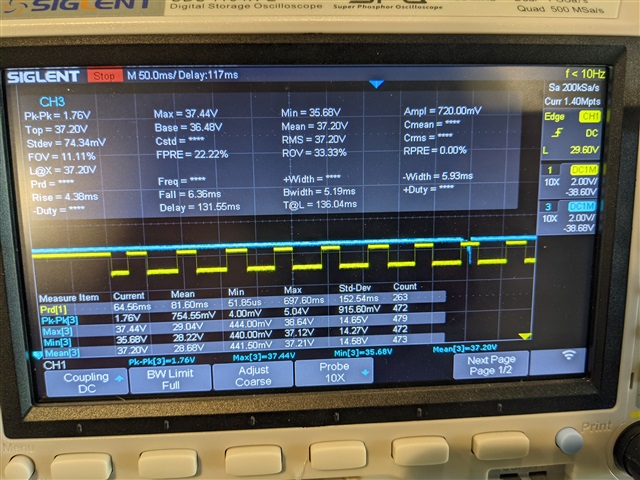

I have set the slow loop to 1,1 which is 1/8th speed.

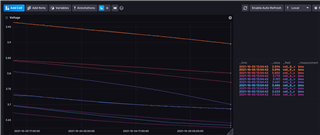

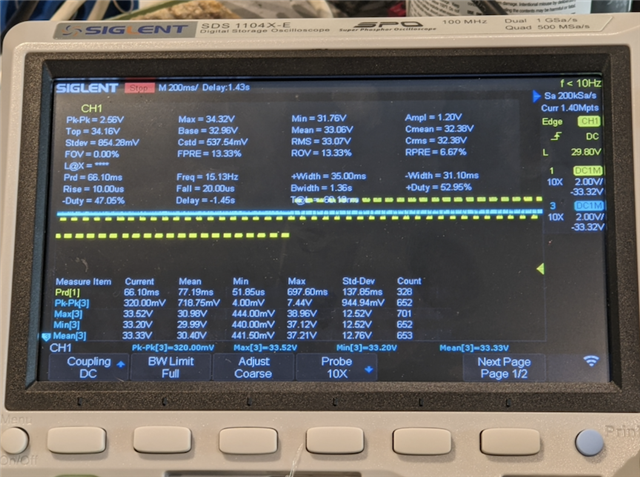

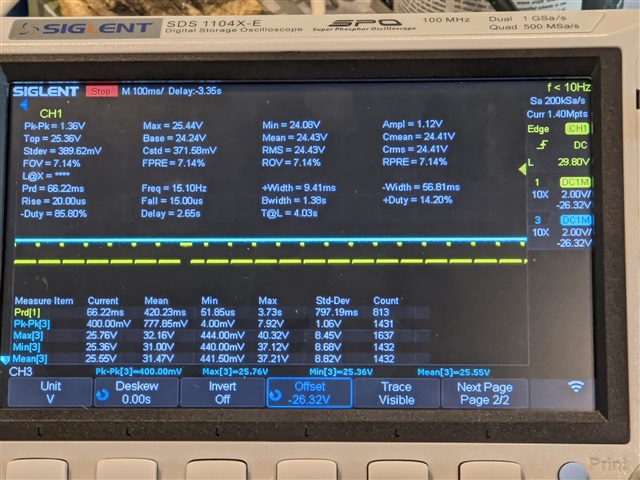

Autonomous balancing seems to always restrict top cell balancing current (both observed and reported through the balance seconds per-cell query) to less than half of other cells.

Do we know what might cause top cell to get lower balancing time than other cells?