Hi Team,

There is a good new that DIN LP87524JRNFRQ1!

1. Please help check this SCH, THX

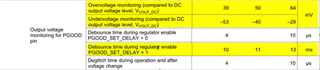

2.Please help confirm why the voltage of LP87524JRNFRQ1 VANA and VIN_B0~3 is reduced from 4.0V to 3.9V. What factors can cause LP87524JRNFRQ1 PGOOD to become LOW?