Other Parts Discussed in Thread: TPS65218

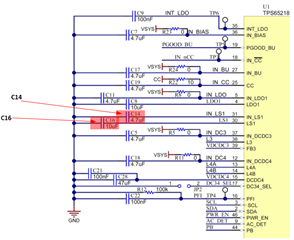

Some of the pins are not used in the design. How should they be connected:

1. DCDC2 is not used in design. But PGOOD state depends on DCDC2 and PGOOD is used.

Would this be ok as DCDC2 connection ? (to save some PCB space)

- connect IN_DCDC2 to VIN and omit the input capacitor

- leave L2 output floating

- connect FB2 to 3.3V from DCDC4 (directly or via voltage divider)

- voltage on FB2 input would then satisfy PGOOD (overvoltage doesn’t matter as STRICT=0b and overvoltage is not monitored)

2. LS2, LS3 not used (TPS6521845 not configured via I2C in design)

- connect IN_LS2, IN_LS3 to GND and leave outputs LS2-3 floating?

3. LS1 not used (but LS1 is enabled by sequence)

- connect IN_LS1 to GND an leave output LS1 floating?

- or connect IN_LS1 to voltage greater than 1.2 V ? (as LS1 is not disabled and 1.2 V is the minimum operating voltage for LS1)

4. LDO1 not used but PGOOD state depends on LDO1 and PGOOD is used.

- connect IN_LDO1 to VIN and omit input and output capacitor