Other Parts Discussed in Thread: BQ76PL455A-Q1

Hi,

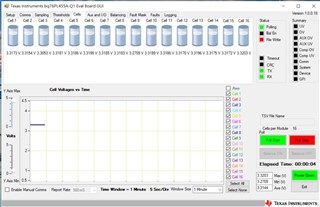

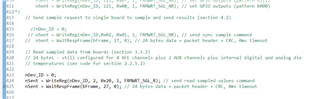

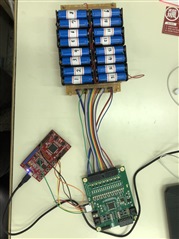

I am trying to program the TMS57004 Launchpad with the sample code provided by TI to work with the BQ76PL455EVM.

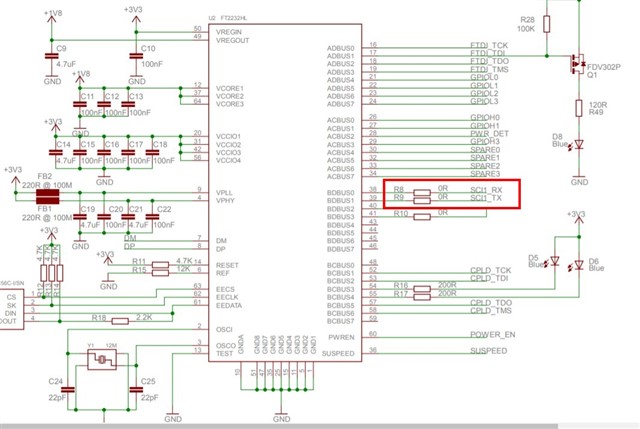

I see the "NOTE: Make sure that the resistor R8 is removed on the TMS570 Launchpad board."

I have a question : I found that the circuit diagram R8 in the design document is 0 ohm. After removing it, the circuit is open, right?

If I remove the R8 in my TMS570 Launchpad , it can work regular when I use BQ76PL455EVM to connect TMS570 ? or I should short circuit?

Could you tell me why should do that.

Very Thanks.