Other Parts Discussed in Thread: RM48L952,

Hi Ti,

We are working safety application that is compliant to IEC-61508 SIL3. And we are having the following doubts on our watchdog implementation for 99% of diagnostic coverage.

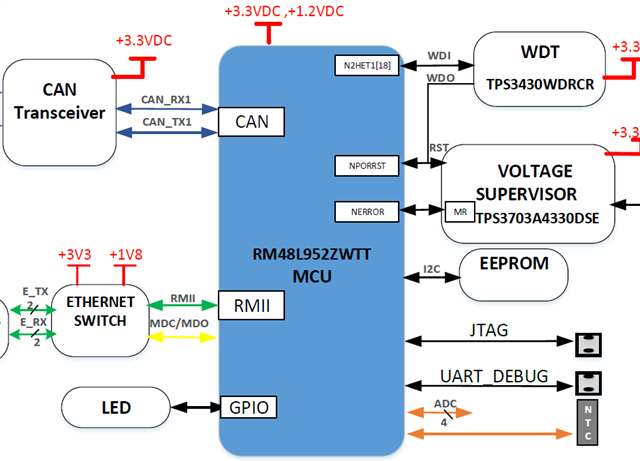

In our design, we are using TPS3430WDRCR IC where the WDI pin of watchdog IC is toggled from MCU (RM48L952) periodically within the watchdog timeout in order for WDO to not assert. Below are our questions on the IC,

I. Whether this IC has a separate time base and time window?

ii. How to implement logical monitoring of the program sequence?

iii. How to implement a combination of temporal and logical monitoring of program sequence?

Whether by using the above-mentioned watchdog IC, is it possible to achieve diagnostic coverage of 99%, which is required for SIL3.

Thanks and Regards,

Monish P