Hi experts,

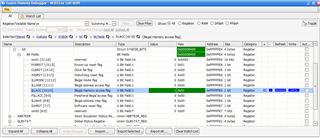

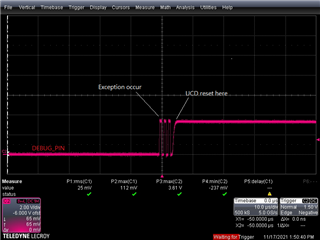

- I encounter an issue that pmbus is not responding after running the application for few days. Since pmbus_handler() is in the background loop, so I add a DEBUG_PIN toggle in the background loop and find DEBUG_PIN stop toggle when pmbus is not responding.

- Meanwhile, when pmbus is not responding (and background loop DEBUG_PIN stop toggle), functions within timer interrupt is still working.

- I also tried to add DEBUG_PIN toggle within all while loop, but DEBUG_PIN is not toggle when issue occur. (I guess this means background loop is not stuck in the while loop.)

- Is there any thing that may cause this issue, the background loop stopped after running for few days?

- It's really weird. Any suggestion would be very helpful. Thanks in advance.