Other Parts Discussed in Thread: TL431

TI,

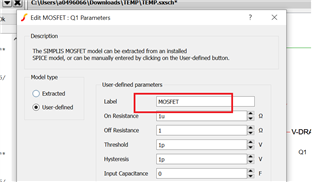

Starting from the ucc28740 simplis simulation example:

https://www.ti.com/product/UCC28740#design-tools-simulation

I created a primary (DC input, switch, clamp, bleeder, etc.), auxiliary (to power the ucc28740) and secondary (power output only), copy and pasted the ucc28740 "symbol" then employed the "F11" key to copy and paste the ucc28740 "sub-circuit code" into my new simplis simulation/schematic/file (see attached - not sure if it attached).

Problem:

I am getting a set of errors that do not make any sense (to me):

Errors:

****************************************

<<<<<<<< Error Message ID: 1051 >>>>>>>>

input file C:/Users/dekk0/Desktop/ECEN/9_5527 PE Lab 2/4_Homework/20_Final Design Files/2_Simulations/SIMPLIS_Data/1_PRI_AUX_NO_Cntrls.deck, line 3385:

+ X3= 1.123456789 Y3= 1.123456789

The value of Y3 should be

larger than the value of

Y2 for this device/model.

On SIMetrix/SIMPLIS , Version : 8.50a

*** END SIMPLIS ERROR REPORT ***

First, there is no "line 3385" in the file "SIMPLIS_Data/1_PRI_AUX_NO_Cntrls.deck".

Second, I have no idea what X3 nor Y3 is nor where they are located nor how to begin to resolve this issue.

Would someone please help me resolve this (and I am guessing follow-on) issue(s)?

Thank you,

C

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/196/1_5F00_PRI_5F00_AUX_5F00_NO_5F00_Cntrls.sxsch

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/196/1_5F00_PRI_5F00_AUX_5F00_NO_5F00_Cntrls.sxsch