Other Parts Discussed in Thread: LM3409

Hello,

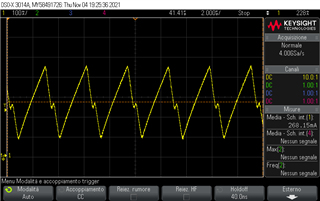

we are experimenting unexpected second toff using LM3409HV.

The schematic is reported below, please note that R3 is not fitted, then Rsns=0.3ohm.

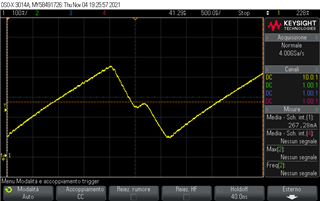

The IADJ pin is controlled to have an avg led current of 350mA. The toff time is around 500ns as expected and the inductor ripple current (around 200mA) is higher than 24mV/Rsns limit of 80mA.

In the scope image the second toff problem reported in the chapter 8.3.4 of the datasheet is present.

Could you please help me to understand why there's a second toff?

Thank you,

Daniele