I am having stability issues with TPS55165-Q1.

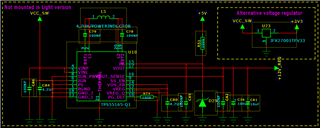

Here is the schematic:

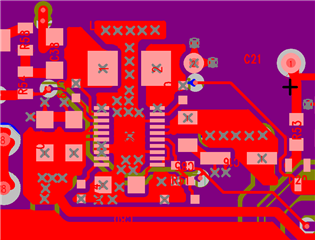

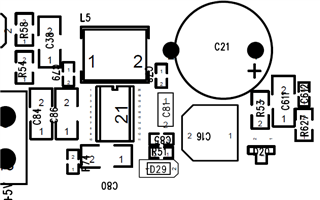

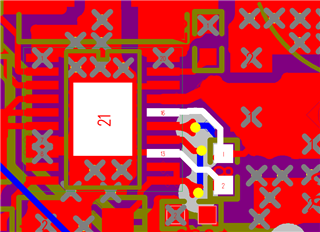

And this is how the layout look like:

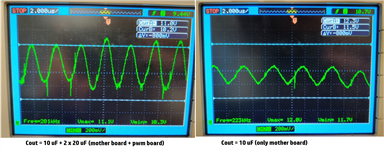

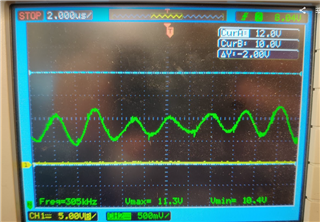

The problem is seen when input voltage is around 11V and higher.

When input is around 11V the output is varying between 10.4V and 11.3V with a frequency of 300Hz.

If starting with an input voltage < 11V and rising, the same "instability" is seen also on higher input voltage. But if starting with input voltage > 11V the output is stable also at higher input voltages.

When searching around in this forum I found out that the layout is very critical. I have already done some layout changes but I'm not sure if these changes will solve my problems (The layout changes have not been tested yet).

The changes are:

* Removed the 100uF electrolyte cap and added 10uF ceramic instead

* Added a 100 nF ceramic cap between pin 16 and 13. See picture below.

Is there anyting else that I can do to improve the layout? I have tried to follow the layout guidlines as good as possible. It seems that the problem is on the boost side.