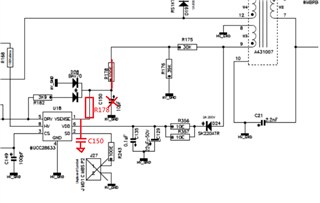

Other Parts Discussed in Thread: UCC28630

Hello,

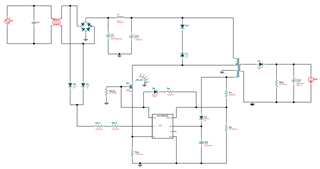

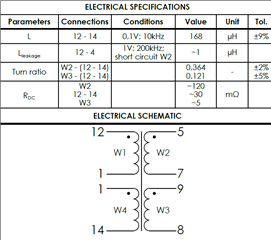

I've made a flyback schematic with the UCC28633.

110VAC to 230VAC input, 40VDC 2A output.

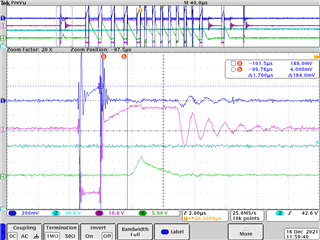

With no load/light load i have the following behaviour.

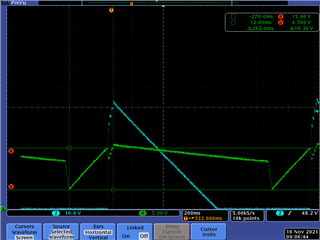

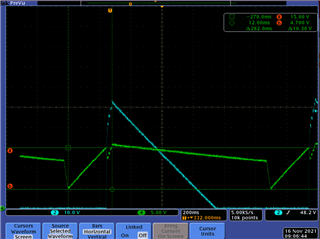

VDD goes up with HV current source.

Line UV check pulses are send.

And switcher starts with normal PWM at 30kHz.

VDD settles around 12V.

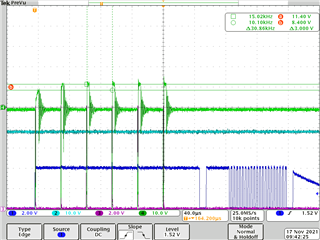

Switcher regulates till Vout is around 40V.

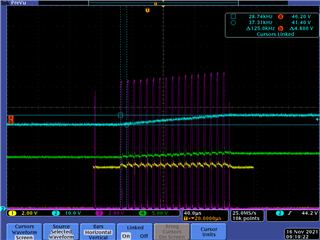

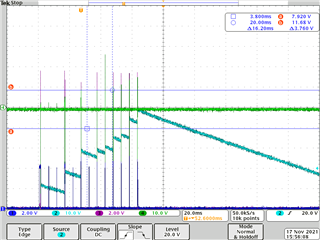

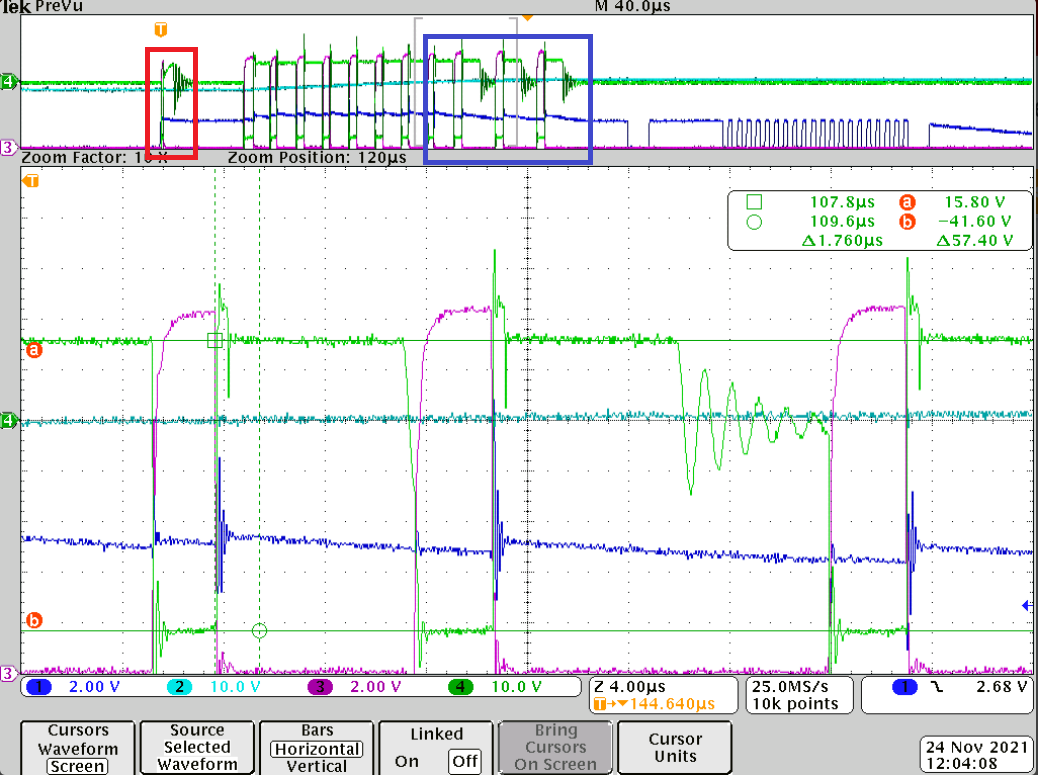

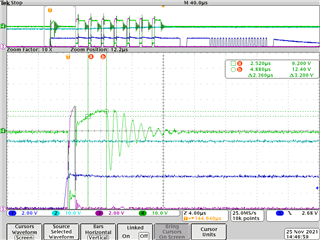

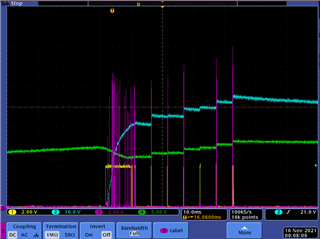

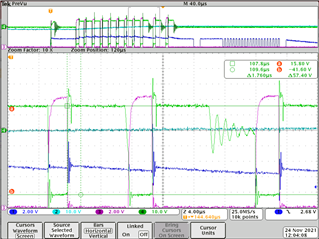

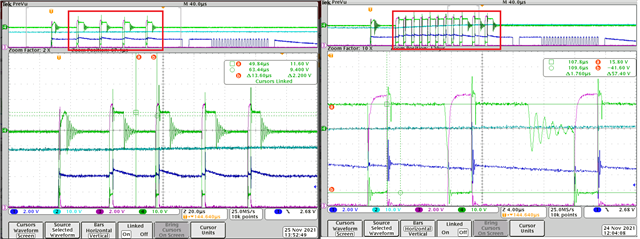

Due to light load, the switcher goes to around 15kHz and goes in sleep mode?

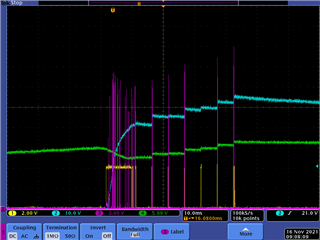

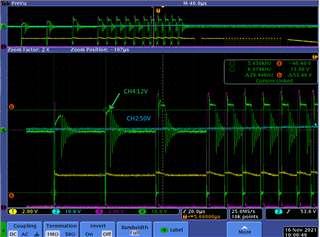

The SD pin goes low for a short while (20us).

The SD pin goes high again for the next switch pulse and remains high for about 45us after the pulse.

Due to the lowering switch frequency the duration of SD low increases.

Last measured time between 2 pulses is 365us or 2,7kHz.

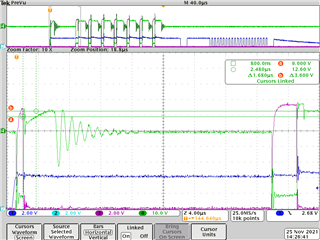

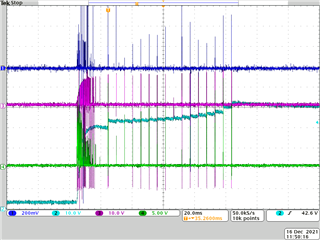

The device goes into a sleep mode?

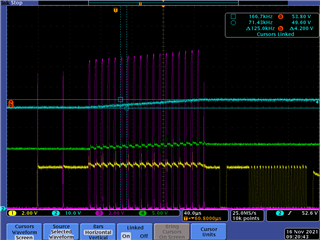

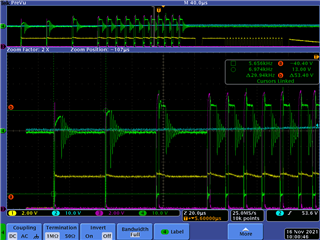

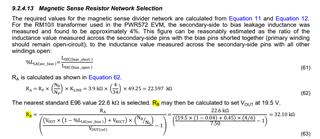

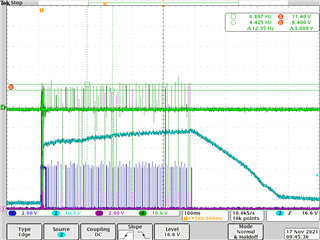

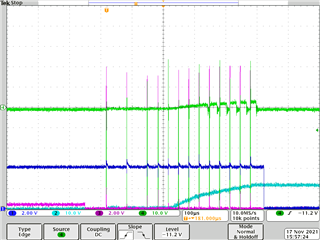

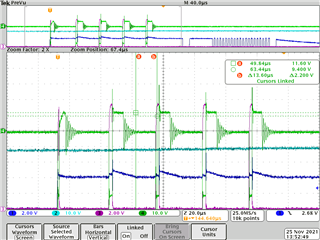

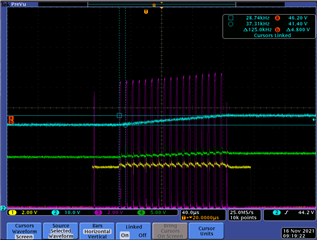

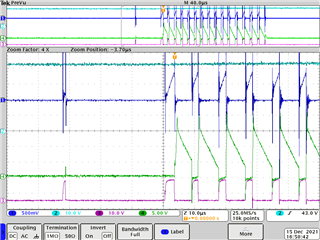

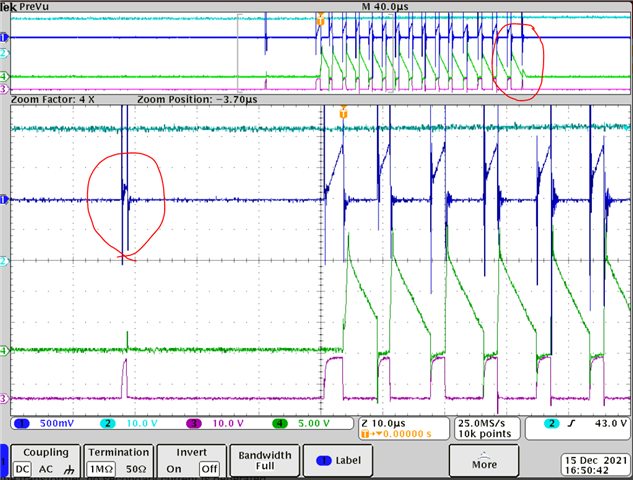

After about 5ms (200Hz) I see the device restart it pulses.

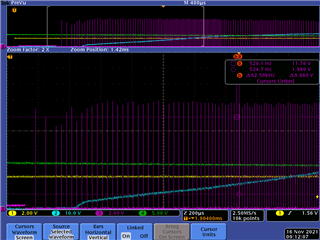

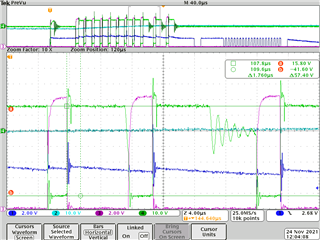

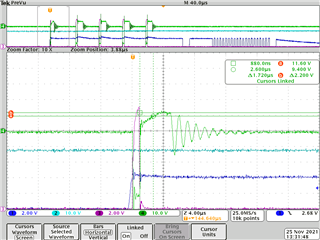

It sends 1 shot pulse (pulse width of 600ns)

It waits for 32us

then sends 17 pulses where Vcs goes to 880mV (pulse width is around 2us)

The frequency of those 17 pulses is 122 kHz

The sequence ends with another short pulse 250ns.

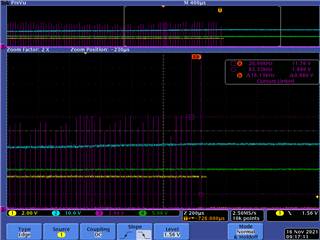

Each time such a sequence happens the output voltage increases.

This lasts until the switcher detects that the Vout is to high and goes in Fault mode with auto restart.

If I increase the output with several whats, the switcher continues to operate.

Can you point me in the derection to optimize my schematic so it works with low loads as well?