Hi team,

I am using UCC28740 in my design of a flyback converter operating in DCM to meet a 24 W load.

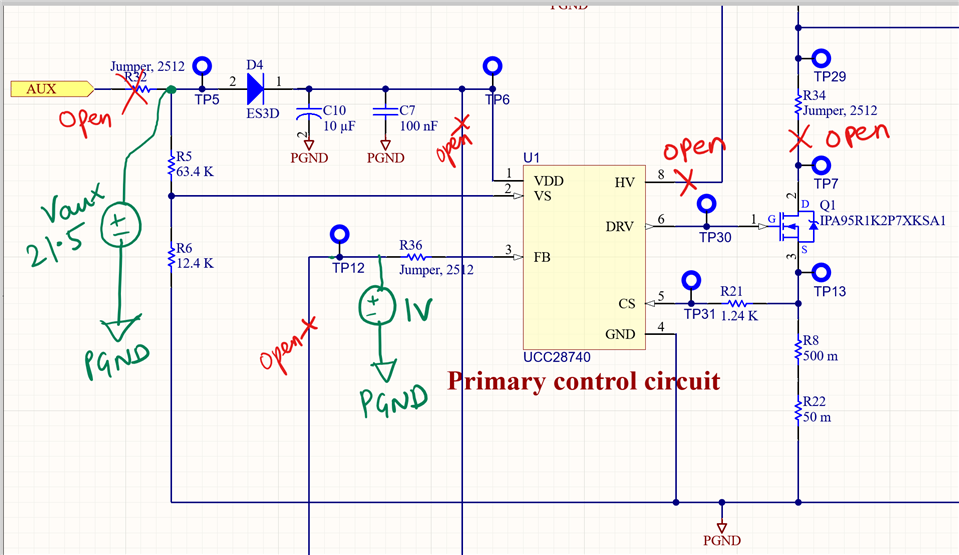

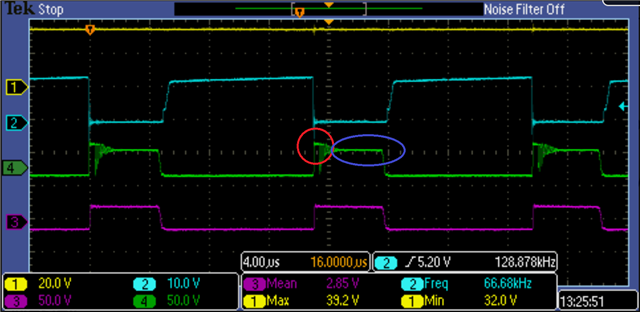

How can I test UCC28740 in an open-loop? I am getting a single pulse at DRV pin when I give 21.5 V at Vaux and no current at the FB pin. I tried giving 1 V across FB pin to feed some uA current but still, the output is a single pulse. How can I get continuous DRV pulses using external power supplies at Vaux and FB?

Are there any guidelines on using UCC28740 in open-loop?

Thanks,

Nanditha