Other Parts Discussed in Thread: TPS3850

Hi guys.

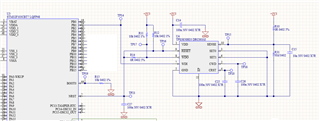

I would like to use the TPS3850-Q1 for:

1) monitor the MCU power supply voltage (overvoltage and undervoltage)

2) une an external watchdog controller

I have only one power supply for all circuits (MCU, TPS3850-Q1 and others): 3.3V.

The microcontroller (STM32F103) does not have the NMI pin; it only has the RESET pin (NRST).

Is the schematic in the picture attached correct?

Can you explain to me how the TPS3850-Q1 works at startup, when power is applied to the board?

How do the WDI and WDO pins behave at startup?

Thanks!

Gabriele.