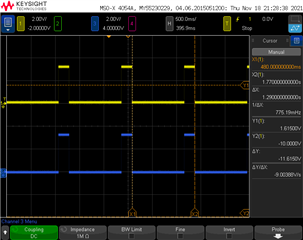

WDO is asserted (logic low) even after giving WDI pulses within timeout (1.6 sec) using GPIO pins of STM32.

It is also asserted while SET1 pin is forced low.

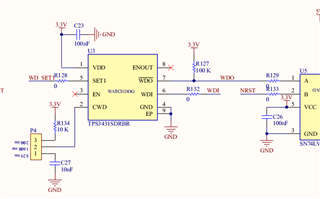

Please find attached schematic for my custom board and oscilloscope screenshot (blue=WDI; yellow=WDO).

My pseudocode for enabled watchdog is as follows:

SET1=1; wait for 100ms;

WDI=0;

while(1)

{

drive WDI=1; wait for 200 ms;

drive WDI=0; wait for 1000 ms;

}

Is there any chance of partial damage to IC or somewhere I am missing.

I have single board to test. Moreover when keeping SET1=1 and keeping WDI=1 continuously then WDO becomes high for 1.6 sec and then low for 200 ms and then again high for 1.6 sec. This waveform repeats so I don't think IC failure might have happened.