Other Parts Discussed in Thread: UCD90320, UCD9090A, UCD90160

I have questions about 2 different UCD90xxx Features

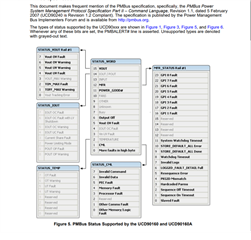

Feature 1: Alert Signal

On a system with 2 UCD90160s, we see the ALERT signal (combined from both devices) from the devices asserted approximately every 60 seconds for 25ms. We believe the cause is an Invalid Command as reported by the CML register - command 0x8D occurs approx every 60 seconds. That is, the Read_Temp1 command which, according to the manuals, is not supported on the UCD90160A.

Questions:

1. Is this the expected behavior for an invalid command? That is, the alert asserts for 25ms and then de-asserts on its own?

2. Does a read of register 0x8D cause an alert to be asserted on the UCD90160A device? What should be the duration of the alert?

3. With this condition occurring, if read_vout register is read for all rails, the alert assert stops.

Why does the alert stop, if the invalid command is still occurring and no ARA msg is sent?

4.If we access the 0x8D register via "i2cget -y -f 13 0x67 0x8D", there is no alert asserted. Why?

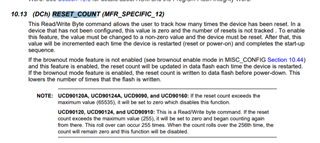

Feature 2: Reset Count

We want to use the reset count feature but see different behavior to enable the feature on different UCD90xxx devices.

Procedure 1 works on UCD9090A but not on UCD90160A or UCD90320. We have to use procedure 2 to enable the reset count feature on UCD90160A and UCD90320.

Why is there a difference?

UCD9090A

Procedure 1:

- echo 1 > rDC

- power cycle the card

- reset count incremented as expected

UCD90160A, UCD90320

Procedure 1 does not work, we have to do these steps

Procedure 2

- echo 1 > rDC

- warm reboot

- the reset count rDC still 1 as expected

- power cycle card

- reset count incremented as expected

Also, is there a way to disable this feature once it's enable?

If yes, can it be reset back to zero?