Hello TI Experts,

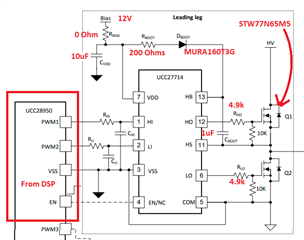

I am Using UCC27714 IC for my Totem pole line synchronous Mosfet Switching. The Resistors and capacitors values are marked in the below figure

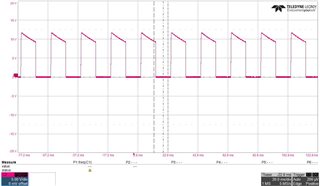

The HO PWM obtained is given below

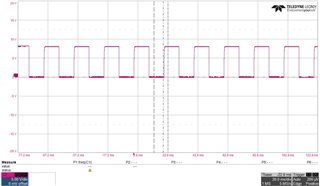

Why there is a slop present in the top side of the PWM ?? also the LO PWM obtained is a perfect square shaped one but do not have the magnitude of 12V

LO PWM

Device Used : STW77N65M5

Diode : MURA160T3G

Switching Frequency : 50Hz (AC Line Frequency)

I am expecting a good support from ur side to sort out my issue !!!