Hi team,

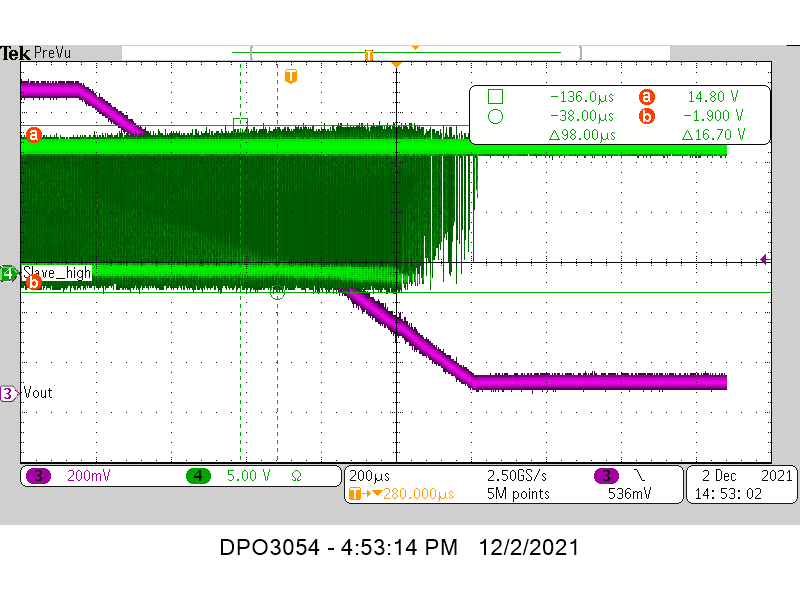

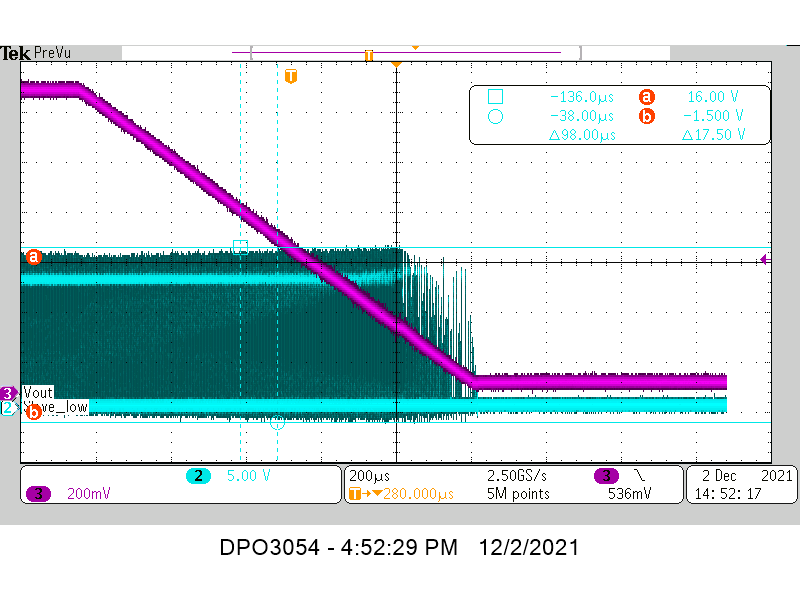

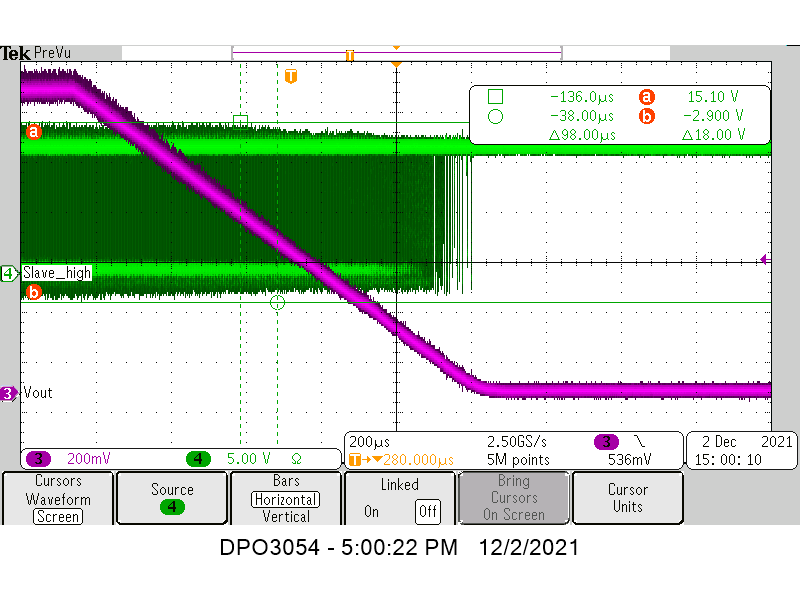

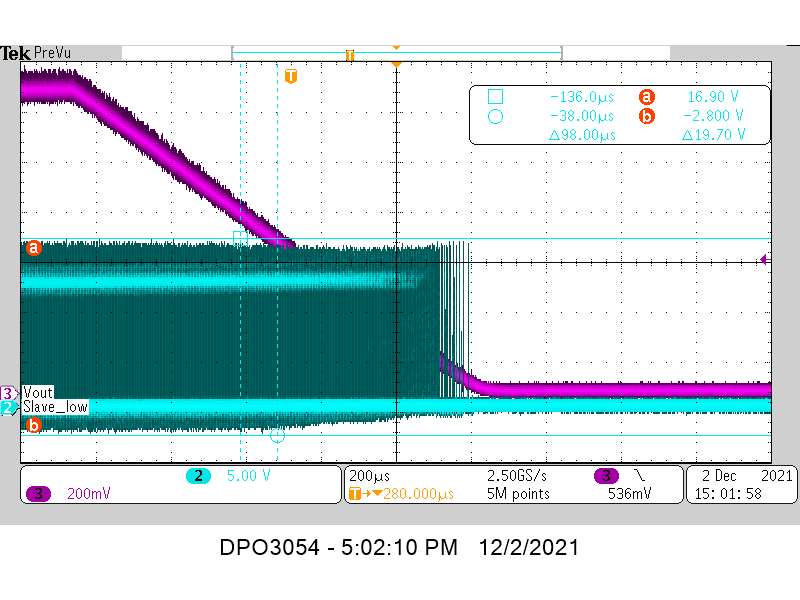

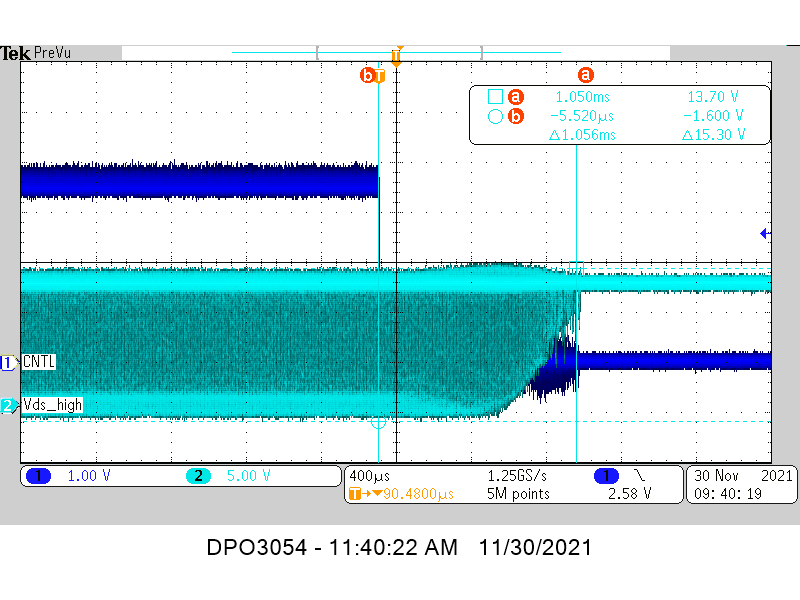

I test the TPS546C23EVM, control the CNTL pull down to disable the output of TPS546C23, and test the Vin to SW(High Mos Vds)

Seeing that the output has a soft shutdown of 1ms, and the 500us Vds has also increased in the end, so I want to confirm what our soft shutdown control mechanism is, and why the High Mos Vds will increase?

Best regards,

Andy Liu