- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Expert,

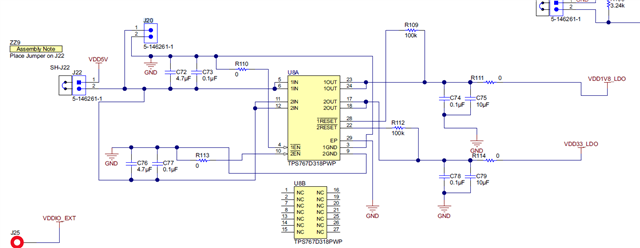

I see TPS767D318PWP is used for supplying DS90UB921AS-Q1 in its reference design. You can see the TPS767D318PWP part as below. As required, the 3.3V cannot be applied earlier than 1.8V. In this design, I don't see the delay part. So how could it guarantee 3.3V will not be applied earlier than 1.8V, since the delay on circuit is random?

Thanks for your support!

BR,

Elec Cheng

Hi Elec,

I do not see a specific delay for the 2 different voltage rails in this schematic either. I'm sending this question to the owners of the DS90UB921-Q1EVM who can assist further.

Thanks,

Stephen

Hello Stephen,

The 921 EVM is set up by default for 3.3V VDDIO where the supplies ramp together. For VDDIO 1.8V the best solution to ensure robustness of the design would be to control the ramps to ensure VDDIO comes up before VDD33. You could do this by connecting the 2EN pin to a supervisor IC such as TLV840-Q1 so that once VDDIO ramps, it can enable the 2EN output with 3.3V or you can use two separate converter ICs. TPS767 is just an example

Best Regards,

Casey