Other Parts Discussed in Thread: TL431

Dear all,

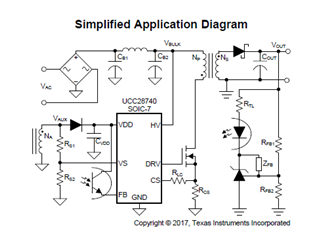

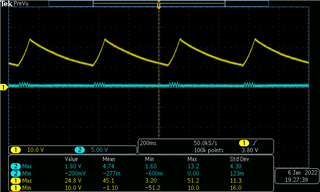

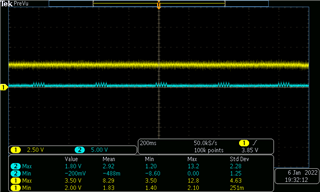

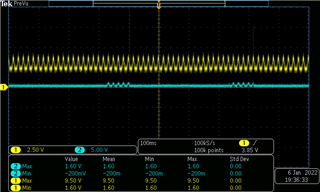

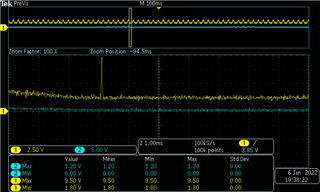

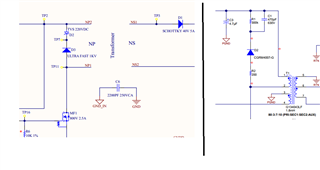

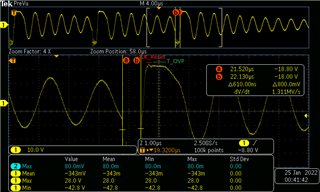

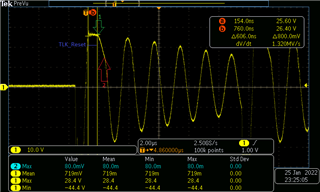

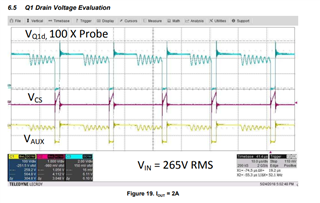

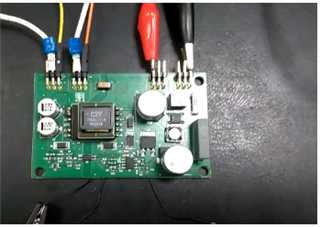

In my project, we are testing a power supply with 3V3 and 2,5A on output circuit.

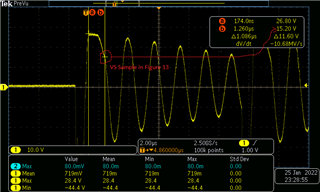

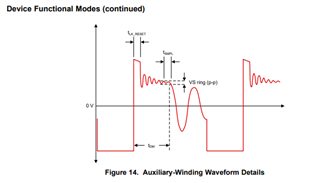

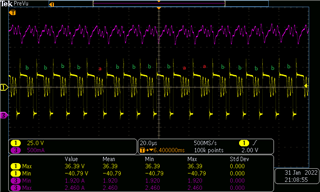

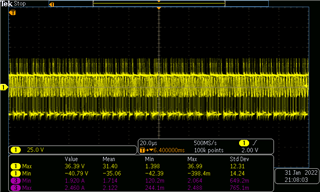

Therefore, the circuit is not switching and we don´t know what is the problem.Following, I am attaching the pictures on testpoints and your measurements. Can technical support help us?

Thank you very much.

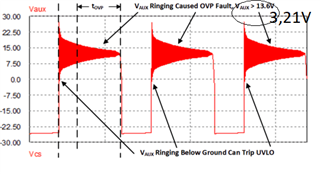

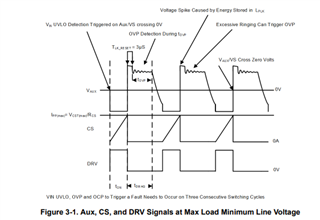

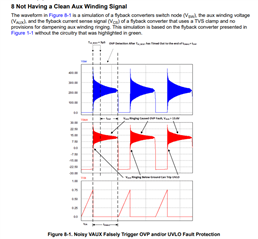

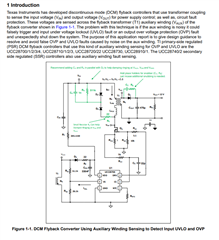

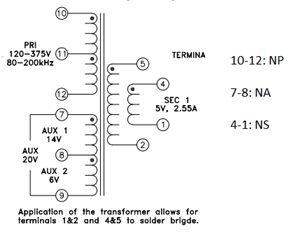

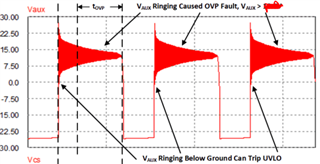

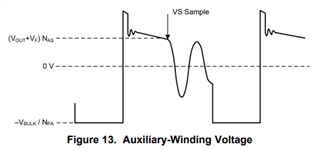

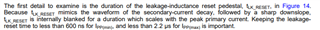

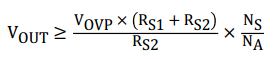

, I have RS1=59k and RS2=68,1k, NS/NA=0.375, because in my project, I design my circuit to operate with 3V3 in outuput voltage (VOUT). Then, using this values resistors, I have Vout>=3,21V. In this context, according to the figure below, my converter was designed to trigger OVP fault protection when VOUT and VAUX were greater than 3,21V. Is this statement correct?

, I have RS1=59k and RS2=68,1k, NS/NA=0.375, because in my project, I design my circuit to operate with 3V3 in outuput voltage (VOUT). Then, using this values resistors, I have Vout>=3,21V. In this context, according to the figure below, my converter was designed to trigger OVP fault protection when VOUT and VAUX were greater than 3,21V. Is this statement correct?