Other Parts Discussed in Thread: TLV7041,

Hi TI experts,

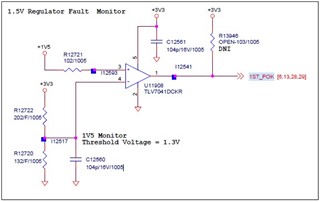

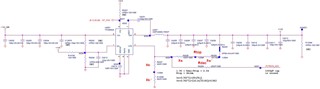

Customer did using TLV7041 + TPS56628. but customer plan to change TLV7041(open drain comparator) to TS2111(normal OPAMP) because of TLV7041 L/T issue.

TPS56628 PG pin and opamp output are connected. TLV7041 is open-drain, so it doesn't matter, but TS2111 is an opamp output.

We are concerned about the internal FET damage of the TPS56628 PG pin.

When 1.5V power is output, OPAMP is output high. However, the PG of TPS56628 hold low.

When the TPS56628 power is output normally, the PG becomes high and the final 1ST_POK net is output as high.

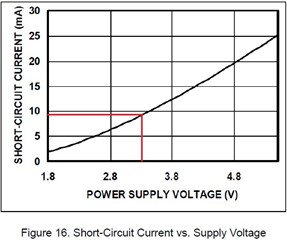

Output current of TP2111 is 20mA.

But PG sink current of TPS56628 is 4mA.

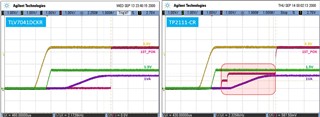

TLV7041 vs TP2111 wave form

If the customer uses TS2111, is there a possibility that the PG pin of the TPS56628 will be damaged?

Please check it.

Thank you.