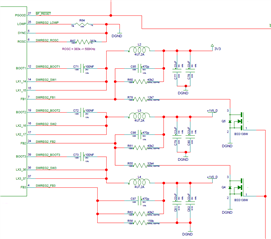

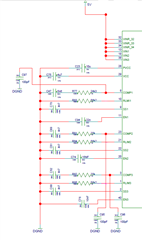

Other Parts Discussed in Thread: TPS65252

We have an application where we generate supply voltages for a Spartan 7 FPGA. This part has some awkward power-on and most especially power-off requirements.

To fulfil the power-off requirements we arrange for the feedback dividers on the 3V3 and 1V8 rails to change to request 0.8V in each case at power-down.

What we expect to see is the charge in the output capacitors flowing back to the supply rail (12V) however and for the 3V3 and 1V8 rails to be brought down to 0.8V very rapidly.

What we see is the 3V3 and 1V8 rails drifting down to 0.8V as if they had been disabled. This is definitely not what is required!

Why do we see this behaviour and what can be done about it?

Please note

- LOW_P is pulled low

- The circuit works with just fine with Richtek's RT7273