Hi team,

Our customer currently has concerns about the LMR33630 SW node spike.

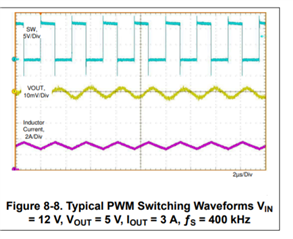

In datasheet Absolute Maximum Ratings, SW to PGND less than 100-ns transients should be between -3.5V to 38V, but in application curves Fig8-8, the negative SW voltage is about -5V. During my tested waveform on EVM, the SW negative spike is also -5.3V which is above -3.5V. Customer is worried about the potential risks of the application, because it is beyond the specification of datasheet. Please help explain this concern and how to resolve it.

Thanks for the support.

BR

Eric Yue