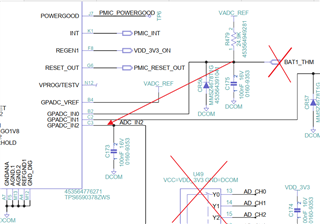

Hi, I want to understand the input impedance of the ADC module, especially in GPADC_IN2.

From my experiment, it turns out the GPADC_IN2 channel input impedance is only around 50Kohm to ground. We have one 24.9Kohm resistor pull up to GAPADC_VREF(1.25V, we turn the Vref constantly on in software). When I connect the 24.9Kohm resistor another pin to the input of GPADC_IN2, the voltage of the input became 923.6mV(in my understanding it should be 1.25V). And when I started the conversion on GPADC_IN2, I can see th input voltage further drop lowest to 830.3mV(last for 549us) , which indicated this channel's input impedance is even lower during the conversion.

Is this an expected behavior on GPADC_IN2? How shall I manage this input voltage drop?