Hi,

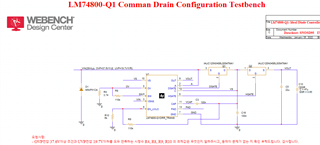

The customer accepted the advice and revised the schematic.

Please review the customer schematic.

OVP : 37.6V

UVLO : 19.7V

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Cho,

Please see my schematic review comments below,

1. The FET selected is only 40V rated. If this is an Automotive application, we would recommend using at least 75V rated FETs are recommended along with SMBJ28A and SMBJ58A connected back-back at the input. For more understanding on this topic, please refer to '11.3 TVS Selection for 24-V Battery Systems' section of the datasheet.

2. With 110 kohms and 6 kohms resistor ladder on the EN/UVLO pin, the EN rising threshold = 23.79V and the EN falling threshold = 21.88V

With 110 kohms and 3.74 kohms resistor ladder on the OV pin, the OV rising threshold = 37.4V and the OV falling threshold = 34.36V

Sorry for the delay in response.

Hi Cho,

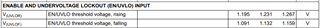

It is a simple resistor divider network. So, the calculation is straight forward.

For example, lets take EN/UVLO. There is a resistor divider from Vin to GND. R9 = 110 kohms, R10 = 6 kohms.

To calculate the EN/UVLO rising threshold,

Vin (R10/(R9+R10)) = 1.231 V

Vin (6k/( 110k + 6k)) = 1.231 V

Vin = 23.79V

To calculate the EN/UVLO falling threshold,

Vin (R10/(R9+R10)) = 1.132 V

Vin (6k/( 110k + 6k)) = 1.132 V

Vin = 21.8 V