Other Parts Discussed in Thread: TPS25750, ALLIGATOR

Hello everyone,

I'm building a power delivery PCB solution for a system that takes USB-C power and outputs 5V to a couple of devices.

For the USB-C PD I'm using TPS25750D and it is configured to output 15V.

For the 5V conversion I'm using a BUCK converter I found using the WEBENCH from TI.

This is the diagram I started with https://webench.ti.com/appinfo/webench/scripts/SDP.cgi?ID=57ADCB5E2ED55CBA

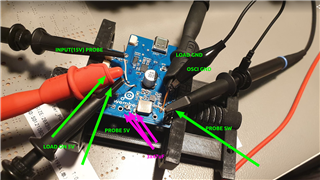

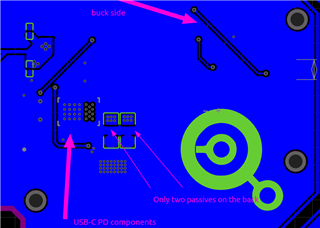

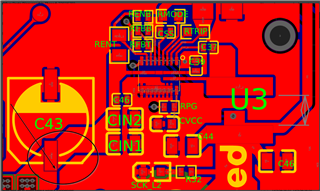

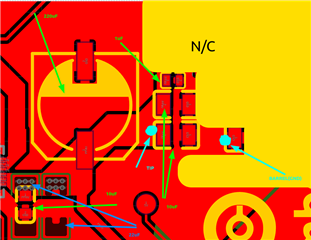

And this is my diagram. See the BUCK circuit on the right corner.

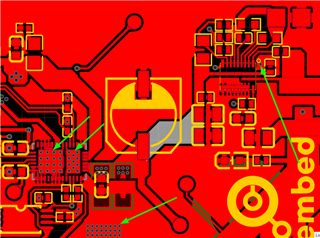

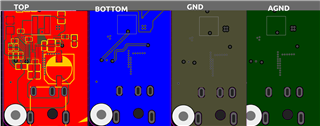

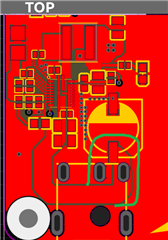

Here's the board layout for the buck converter. This is a two-layer board

With this all in mind here's what's happening:

When I assemble everything correctly the SCK_L turns on and the output of the buck reads 4.93V. This means it converts 15V to ~5V. However, when I attach more load to it, it just melts down and PPHV line, GND and 5V get shorted together internally (checked for shorts on the chip itself). Note that I don't attach more load while it's on as in a hotplug and the loads that I attach are working fine otherwise (tested with a different power supply).

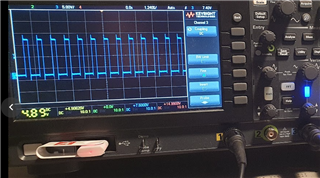

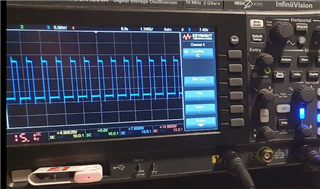

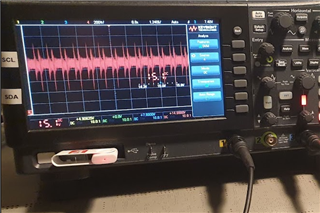

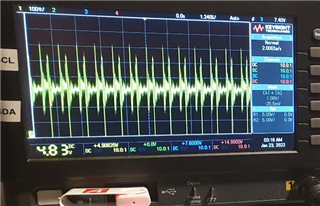

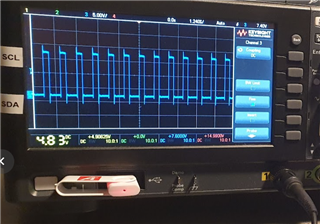

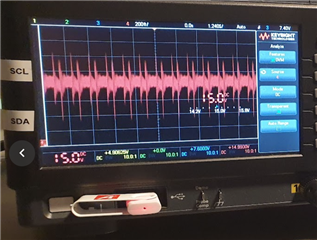

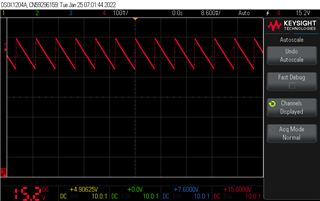

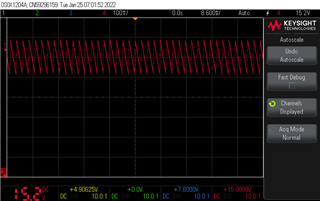

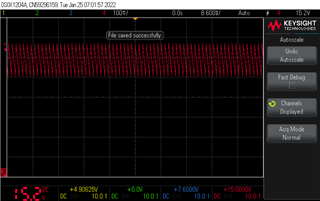

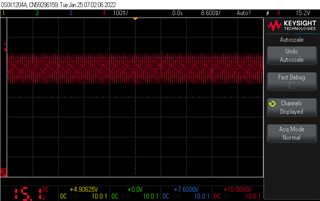

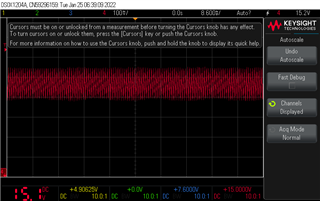

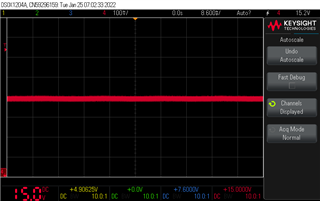

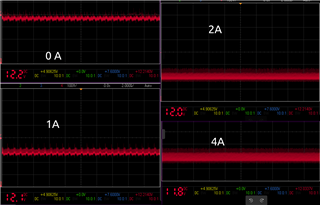

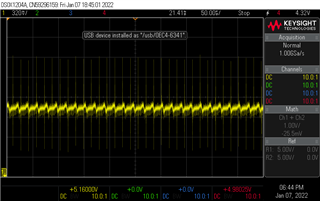

Now I did a different test using an external power supply trying to power up the buck converter (through the pads of C43 capacitor). It turns on even with loads, however, the main load which probably draws more than 1A reports risky low voltage. A multimeter will report 4.92-4.93V. Here's an oscilloscope reading:

I'm not sure what else to say. Please ask questions if something is unclear.

Many thanks,

M.