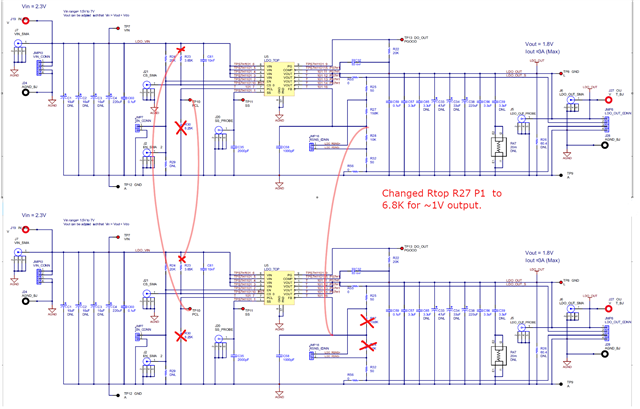

Which if any of the PSpice models (WCA or Transient) support stability/bode plot simulations of 2 LDO’s operating in parallel? If none, is there a way to do a stability/bode plot simulation using a single LDO that would be a good approximation of 2 LDO’s operating in parallel?

Some observations:

- The WCA model seems to be the model prescribed for stability/bode plot simulations but doesn’t appear to have the provisions to support parallel functionality, i.e. no PCL nor CS pins.

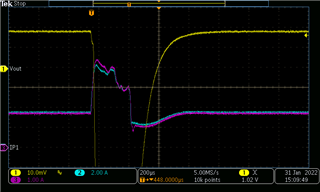

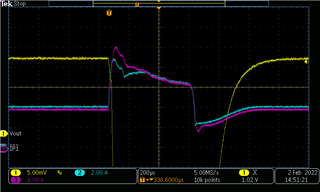

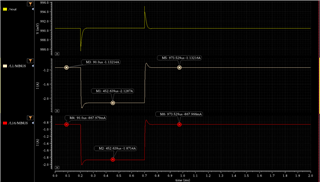

- There is a test-bench in the transient model (Schematic=AC1, Sim Profile=AC-Bode) but when run the simulation profile that comes with test-bench and bode plot template placed at VOUT get anomalous results, see screen shot below.

Please advise, Thank you -John