Other Parts Discussed in Thread: TINA-TI

Hi Gate driver folks,

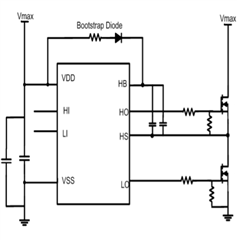

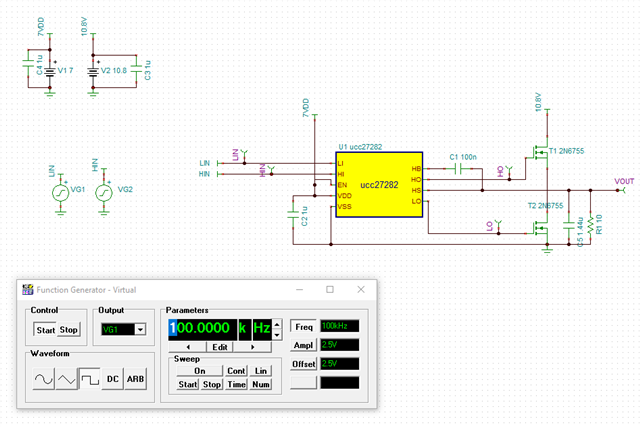

I have two questions during I simulate UCC27282 using TINA-TI. Could you help?

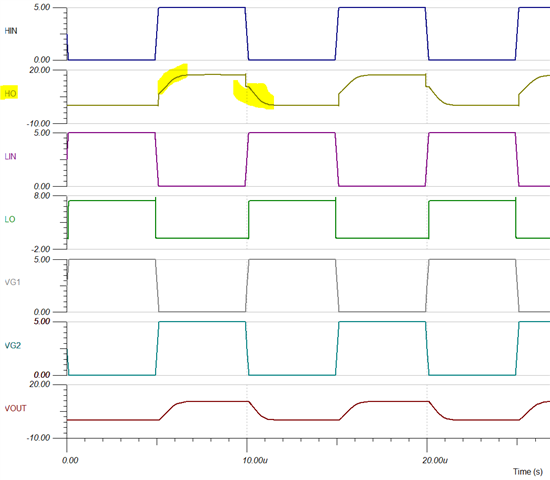

(1) For HO in simulation result, there shows a lump rising&falling edge. It looks it's because the output capacitor (C5 1.44uF) holds the VOUT voltage.

Per datasheet, the lump edges are also present in figure 35~38. Is the lump waveform from the datasheet appearing due to the same reason?

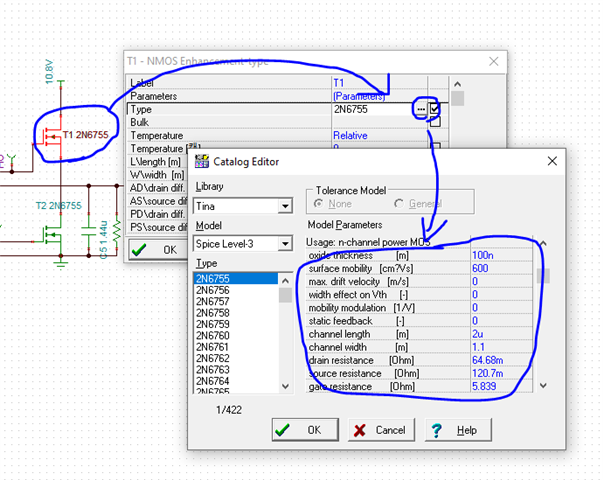

(2) Customer is using FET BSC070N10NS5 with UCC27282. To estimate rise and fall time thru tina simulation, I want to model FETs similar to BSC070N10NS5. I believe the gate charge specification would be the most major factor for rise and fall time. Is my understanding correct?

Then could you advise how to model the transistor similar to the transistor that customer is using? Which parameter should I change?

It would be appreciated if you provide any advice as quick as possible.. Thanks!