Other Parts Discussed in Thread: CSD19535KTT

Hi Gate driver folks,

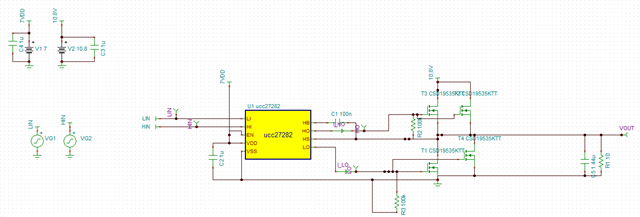

I'm proceeding a tina simulation with UCC27282 and CSD19535KTT. Would you

(1) BST capacitor

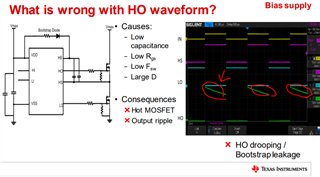

Per page 8 in this material, I expect the HO shows dropping with the small (wrongly selected) BST capacitor. I believe 100~470nF would be proper, but the simulation still works with 10nF of BST capacitor! Even without dropping! The simulation also works with 10uF of BST capacitor! I guess it's not like to happen in bench. Could you advise on its operation? Is the tina simulation wrong?

I want to check the operation of UCC27282 with external circuitry such as gate series resistor, gate input filter, etc.). If the tina model is wrong, do you not recommend to use this tina simulation?

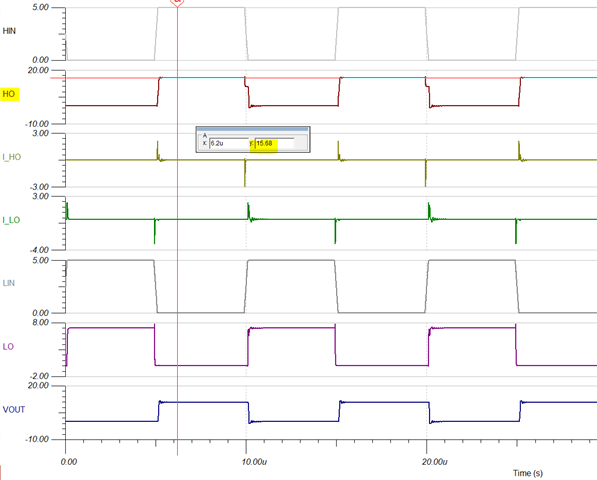

- C_BST = 10nF --> HO = 15.68V

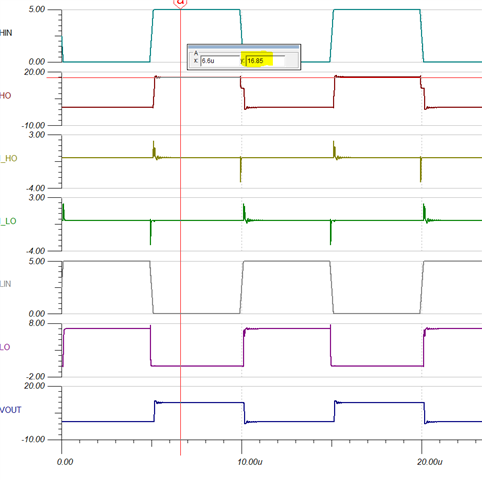

- C_BST = 100nF --> HO = 16.85V

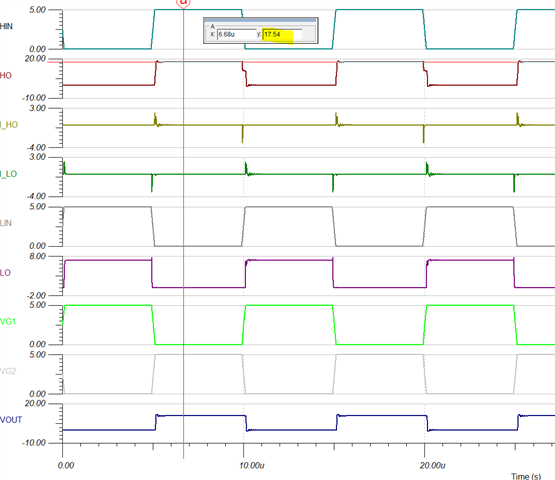

- C_BST = 10uF --> HO = 17.54V

(2) Interlock function

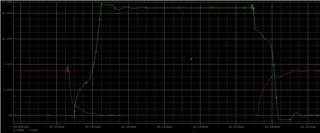

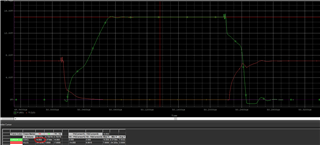

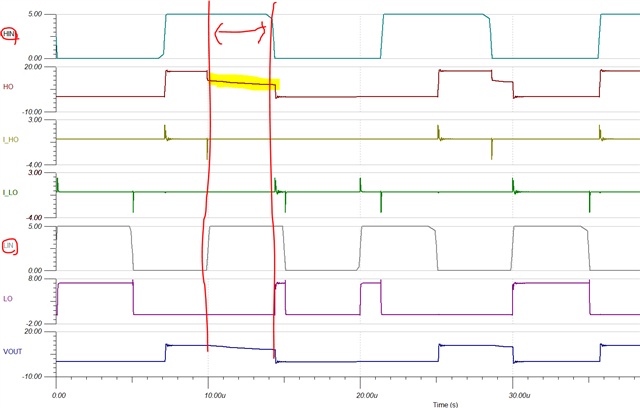

I also want to check the interlock functionality of UCC27282. I set HIN with 70kHz and LIN with 100kHz. During the overlap period (that I marked with red arrow), HO is not fully turned off. Is it what really happen with UCC27282? Could you explain how this waveform appears?

Thank a lot!