TI experts,

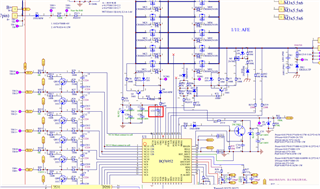

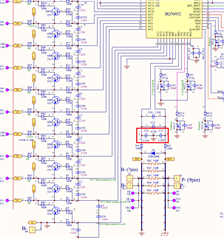

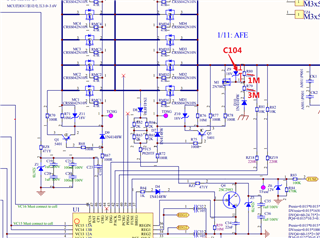

bq76952 project, 14S6P 30Ah using LG21700M50LT cells,

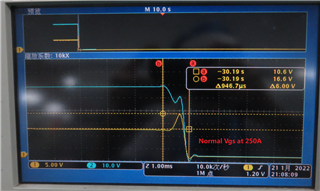

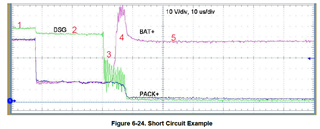

I use the load to discharge the battery pack 250A, trigger the SCD protection, the Vgs waveform of the MOSFET looks normal.

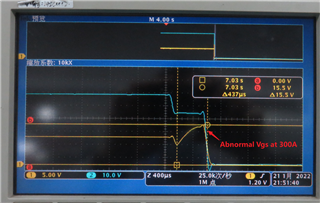

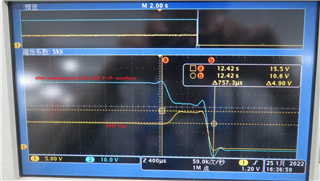

But when we increase the current to 300A, trigger the SCD protection,

the Vgs waveform of the MOSFET will first drop to 7.7V, then rise to 15.5V, and finally drop to 0V. What is the reason for this? This can easily burn out the MOSFET.

76952-0-36-10bei-0.2mR-R00-2022-1-10(CRC).gg.csv