Dear TI-er.

What does below mean?

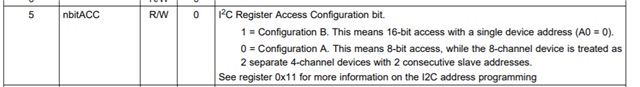

The SRAM and parity programming control must be completed at the lower I 2C address (Channels 1-4). Configuring SRAM control registers for the upper I 2C device address (Channels 5-8) does not program the SRAM or parity.

How to Load TPS2388x SRAM and Parity Code Over I2C