Other Parts Discussed in Thread: LM94022, INA240, , TPS737

Hello forum,

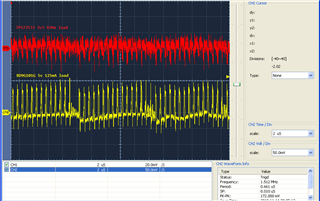

I have system with 2x 73533 LDO regulator input +5v04. One LDO has +3v307 isolated output to feed several discrete TI devices. The other supply MCU (105°C temp range) VDD rail is +2v97 minimum thus has terrible EMI rejection, easily crashes MCU.

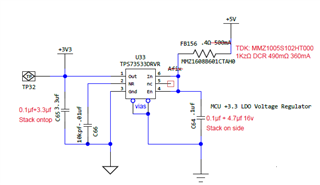

Replacing the LDO (+2v97) made no difference, output into unpowered 4k8Ω rail load, LDO barely gets warm not hot. Oddly same PCB layout for different TI MCU (same class 85°C) maintains +3v309 into unpowered 4K3Ω VDD rail load. Both PCB has same +5v04 150MHz bucking regulator via 1KzΩ, 490mΩ DCR 350mA ferrite with 4.7uf+100nF(parallel) at the input pin 6. Reducing the ferrite impedance made no difference to LDO output (2v970) hence the higher 1kzΩ now remains. The LDO digital ground pin plane is some-what isolated from larger buck regulator analog ground plane via FB1 (0Ω <50mohm) resistor to further reduce EMI on +3v3 rail feed to MCU.

Yet the higher temperature MCU class (105°C) VDD rail (4K8Ω) appears to pull LDO output down to +2v97 causing terrible PSRR and poor rejection of EMI. The LDO output has 3.3µF+100nF (parallel) - even replaced with 4.7µF made no difference, output remains +2v97 in the EMI danger zone of the MCU.

What to look for cause of LDO with +2v97 output anomaly?