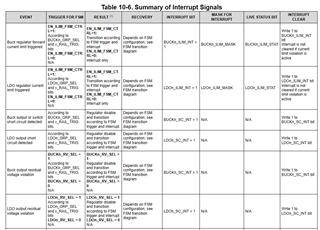

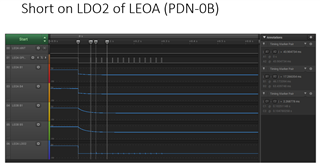

We need to mask UV/OV/residual detection of Vin/Vout which will lock the die .How can we mask the detection ?

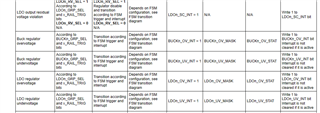

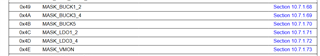

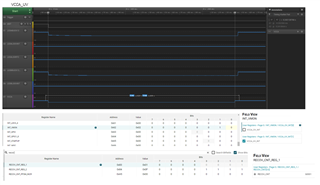

VCC OV/UV: 0X4E ,is it right?

VCC residual voltage :how to mask ?

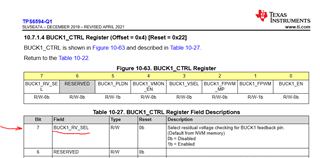

BUCK/LDO vout OV/UV::0x48 /0x49/0x4A/0X4B/0X4C/0X4D ,is it right?

BUCK/LDO vout residual voltage : how to mask ?