HI FAE

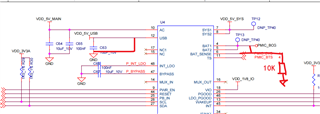

I am using TPS65217 to power AM335x, I would like to know if the PMIC is powered without battery, USB is connected to GND, and powered by AC, I would like to know the detailed requirements for AC input

What is currently understood from the datasheet is that

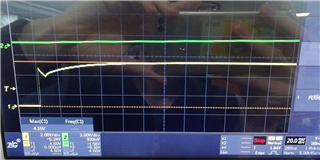

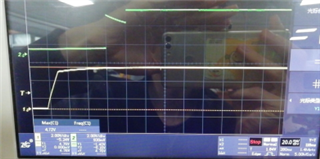

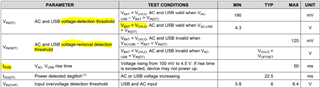

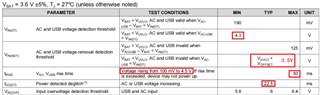

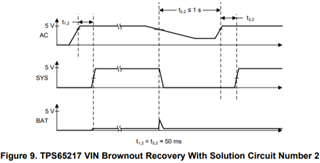

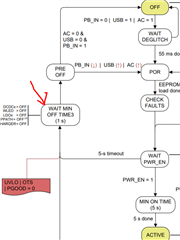

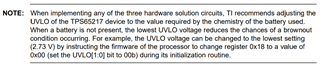

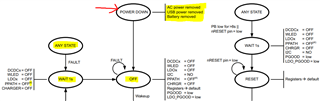

1. AC rise needs to rise above 4.3V within 50mS

2. After the AC rises to 4.3V, after 22.5mS, it will check again whether the AC reaches 4.3V (deburring detection). If it is, the AC will be selected as the power supply to SYS, and the power-on sequence will start.

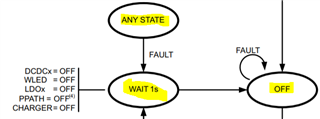

3. After the AC rises to 4.3V, if it drops below 3.5V, it will enter the LOCK state

Is my understanding correct? There are doubts here

1. Is there any requirement for the rising waveform of AC within 50mS? For example: Is it allowed to rise, fall and then rise before 4.3V?

2. For deburring detection, is the judgment standard for the second detection 4.3V or 3.5V?

3. If it drops to 3.5V before deburring detection, will it also enter the LOCK state

Bset wishes